# TIME-TRIGGERED COMMUNICATION

## Edited by ROMAN OBERMAISSER

## TIME-TRIGGERED COMMUNICATION

## **Embedded Systems**

#### **Series Editor**

Richard Zurawski SA Corporation, San Francisco, California, USA

Communication Architectures for Systems-on-Chip, edited by José L. Ayala

Real Time Embedded Systems Design and Analysis with Open-Source Operating Systems, *Ivan Cibrario Bertolotti and Gabriele Manduchi*

Time-Triggered Communication, edited by Roman Obermaisser

## TIME-TRIGGERED COMMUNICATION

## Edited by ROMAN OBERMAISSER

CRC Press is an imprint of the Taylor & Francis Group, an **informa** business CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2012 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works

Printed in the United States of America on acid-free paper Version Date: 20110629

International Standard Book Number: 978-1-4398-4661-2 (Hardback)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

## **Contents**

| Li | ist of I   | igures                           |                                                     | xvii  |

|----|------------|----------------------------------|-----------------------------------------------------|-------|

| Li | ist of 7   | <b>Tables</b>                    |                                                     | xxiii |

| E  | ditor      |                                  |                                                     | xxv   |

| C  | ontrib     | utors                            |                                                     | xxvii |

| 1  |            | o <mark>ductio</mark><br>bermais |                                                     | 1     |

|    | 1.1<br>1.2 | Scope                            | of the Book                                         |       |

| 2  |            |                                  | epts and Principles of Time-Triggered Communication | 5     |

|    |            |                                  | sser and H. Kopetz                                  |       |

|    | 2.1        |                                  | uction                                              |       |

|    | 2.2        | -                                | n Structure                                         |       |

|    | 2.3        |                                  | pts of Dependability                                |       |

|    |            | 2.3.1                            | Dependability Threats – Failure, Error, Fault       |       |

|    |            | 2.3.2                            | Fault Containment                                   |       |

|    |            | 2.3.3                            | Failure Modes                                       |       |

|    |            | 2.3.4                            | Fault Hypothesis                                    |       |

|    | 2.4        |                                  | Time and State                                      |       |

|    |            | 2.4.1                            | Time and Clocks                                     |       |

|    |            | 2.4.2                            | Precision and Accuracy                              |       |

|    |            | 2.4.3                            | Global Time                                         |       |

|    |            | 2.4.4                            | Sparse Time                                         |       |

|    |            | 2.4.5                            | State of a System                                   |       |

|    | 2.5        |                                  | omous Control of Communication Networks             |       |

|    |            | 2.5.1                            | Types of Temporal Control Signals                   |       |

|    |            |                                  | 2.5.1.1 Event Triggers                              |       |

|    |            | 252                              | 2.5.1.2 Time Triggers                               |       |

|    |            | 2.5.2                            | Information Semantics                               |       |

|    |            | 2.5.3                            | Temporal Firewall                                   |       |

|    |            | 2.5.4                            | Transport Protocols                                 |       |

|    |            | 2.5.5                            | Flow Control                                        | . 23  |

|   | ٠ |

|---|---|

|   | 1 |

| v | I |

|   |   |

| -     | maisser and I | Triggered Communication Systems                    |

|-------|---------------|----------------------------------------------------|

|       |               | · · · · · · · · · · · · · · · · · · ·              |

|       | omposability  |                                                    |

|       |               | nent-Based Design                                  |

|       | *             | •                                                  |

| 5.    | I I I         | hent Interfaces                                    |

|       | 3.2.2.1       | Linking Interface                                  |

|       | 3.2.2.2       | Technology Independent Interface (TII)             |

|       | 3.2.2.3       | Technology Dependent Interface (TDI)               |

| 2     | 3.2.2.4       | Local Interface                                    |

|       |               | Interface Specification                            |

| 3.    |               | sition of Nodes                                    |

|       | 3.2.4.1       | Independent Development of Nodes                   |

|       | 3.2.4.2       | Stability of Prior Services                        |

|       | 3.2.4.3       | Non-Interfering Interactions                       |

|       | 3.2.4.4       | Preservation of the Node Abstraction in the Case   |

|       |               | of Failures                                        |

|       |               | d Predictability                                   |

|       |               | ncept of Determinism                               |

| 3.    |               | Determinism                                        |

|       | 3.3.2.1       |                                                    |

|       | 3.3.2.2       | Deviations of Computational Progress Relative to   |

|       |               | Real Time                                          |

|       | 3.3.2.3       | Oscillator Drift                                   |

|       | 3.3.2.4       | Preemptive Scheduling                              |

|       | 3.3.2.5       | Nondeterministic Language Features                 |

| 3.    | 3.3 Buildin   | g a Replica Determinate System                     |

|       | 3.3.3.1       | Sparse Time-Base                                   |

|       | 3.3.3.2       | Agreement on Input                                 |

|       | 3.3.3.3       | Static Control Structure                           |

|       | 3.3.3.4       | Deterministic Algorithms                           |

|       | 3.3.3.5       | Deterministic Communication System                 |

| 3.4 D | iagnosability |                                                    |

| 3.    | 4.1 Detection | on of Errors and Anomalies                         |

| 3.    | 4.2 Decisio   | n Making – Analysis of Diagnostic Information      |

| 3.    | 4.3 Use of 1  | Diagnostic Information and Analysis Results        |

| 3.5 C | ertifiability |                                                    |

| 3.    | 5.1 Safety (  | Case                                               |

| 3.    |               | r Certification                                    |

| 3.    |               | ation in Application Domains                       |

| 3.    |               | riggered Communication Protocols and Certification |

|       |               | ent and Error Containment                          |

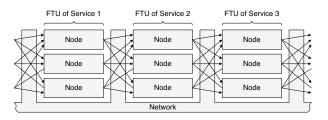

|       |               | dent Fault Containment Regions                     |

|       |               | ontrol on Node Interactions                        |

|       |               | Determinism                                        |

|   |     | 3.6.4    | Recovery and Repair                                         | 17       |

|---|-----|----------|-------------------------------------------------------------|----------|

|   | 3.7 | Perform  | mance                                                       | 8        |

|   |     | 3.7.1    |                                                             | 8        |

|   |     | 3.7.2    | Performance Attributes                                      | 9        |

| 4 | Cor | e Algori | ithms 5                                                     | 53       |

| - |     | 0        | a, W. Steiner, R. Obermaisser and C. El Salloum             | 5        |

|   | 4.1 |          |                                                             | 54       |

|   | 4.1 |          |                                                             | 55       |

|   | 4.2 | 4.2.1    | J                                                           | 56       |

|   |     | 4.2.1    |                                                             | 57       |

|   |     |          | 5                                                           | 57<br>57 |

|   |     |          |                                                             |          |

|   |     | 4.0.0    | e                                                           | 8        |

|   |     | 4.2.2    |                                                             | 59       |

|   |     | 4.2.3    | Limits in and Performance of Clock Synchronization Algo-    |          |

|   |     |          |                                                             | 51       |

|   |     | 4.2.4    |                                                             | 51       |

|   |     | 4.2.5    |                                                             | 55       |

|   |     |          |                                                             | 55       |

|   |     |          |                                                             | 66       |

|   |     | 4.2.6    | 1 11 1                                                      | 57       |

|   | 4.3 | -        |                                                             | 58       |

|   |     | 4.3.1    |                                                             | 58       |

|   |     | 4.3.2    | 1                                                           | 0        |

|   |     |          | 8                                                           | 1        |

|   |     |          |                                                             | 4        |

|   |     | 4.3.3    |                                                             | 7        |

|   |     |          | 1 6                                                         | 8        |

|   | 4.4 | Integra  | ation of Event-Triggered and Time-Triggered Communication 8 | 80       |

|   |     | 4.4.1    | Integration of Event-Triggered and Time-Triggered           |          |

|   |     |          | Communication at MAC Layer                                  | 81       |

|   |     |          | 4.4.1.1 Event-Triggered and Time-Triggered                  |          |

|   |     |          | Communication — Contention Avoidance 8                      | 81       |

|   |     |          | 4.4.1.2 Event-Triggered and Time-Triggered                  |          |

|   |     |          | Communication — Contention Detection with                   |          |

|   |     |          | Preemption                                                  | 32       |

|   |     |          | 4.4.1.3 Event-Triggered and Time-Triggered                  |          |

|   |     |          |                                                             | 33       |

|   |     | 4.4.2    |                                                             | 33       |

|   |     | 4.4.3    |                                                             | 34       |

|   |     |          | 4.4.3.1 Higher Protocols: CORBA Internet Inter-ORB          |          |

|   |     |          | •                                                           | 85       |

|   |     |          | 4.4.3.2 Higher Protocols: Controller Area Network           |          |

|   |     |          | e e                                                         | 35       |

|   | 4.5 | Diagno   |                                                             | 88       |

vii

|   |             | 4.5.1   | Error Detection                                         | 88  |

|---|-------------|---------|---------------------------------------------------------|-----|

|   |             |         | 4.5.1.1 Error Detection by Syntactic Checks             | 89  |

|   |             |         | 4.5.1.2 Error Detection by Semantic Checks              | 89  |

|   |             |         | 4.5.1.3 Error Detection by Active Redundancy            | 90  |

|   |             | 4.5.2   | Membership Agreement                                    | 90  |

| 5 |             |         | ered Protocol (TTP/C)                                   | 93  |

|   | <i>R. O</i> | bermais | sser                                                    |     |

|   | 5.1         |         | col Overview                                            | 94  |

|   | 5.2         |         | col Services                                            | 95  |

|   |             | 5.2.1   | Communication Services                                  | 96  |

|   |             |         | 5.2.1.1 Temporal Structuring of Communication           | 96  |

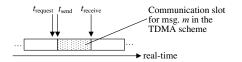

|   |             |         | 5.2.1.2 Timing of a TDMA Slot                           | 97  |

|   |             |         | 5.2.1.3 Frame Types and States                          | 98  |

|   |             | 5.2.2   | Clock Synchronization                                   | 99  |

|   |             | 5.2.3   | Restart, Re-Integration, Integration                    | 100 |

|   |             | 5.2.4   | Diagnostic Services                                     | 101 |

|   |             |         | 5.2.4.1 Life-Sign                                       | 101 |

|   |             |         | 5.2.4.2 Membership Service                              | 102 |

|   |             |         | 5.2.4.3 Clique Detection                                | 104 |

|   |             |         | 5.2.4.4 Communication System Blackout Detection         | 104 |

|   |             | 5.2.5   | Fault Isolation                                         | 104 |

|   |             | 5.2.6   | Configuration Services                                  | 106 |

|   |             |         | 5.2.6.1 Mode Changes                                    | 106 |

|   |             |         | 5.2.6.2 Boot Loader                                     | 107 |

|   | 5.3         | Protoc  | ol Parameterization                                     | 108 |

|   |             | 5.3.1   | Message Descriptor List                                 | 108 |

|   | 5.4         | Comm    | nunication Interface                                    | 110 |

|   |             | 5.4.1   | Status Area                                             | 110 |

|   |             | 5.4.2   | Control Area                                            | 113 |

|   |             |         | 5.4.2.1 Message Area                                    | 114 |

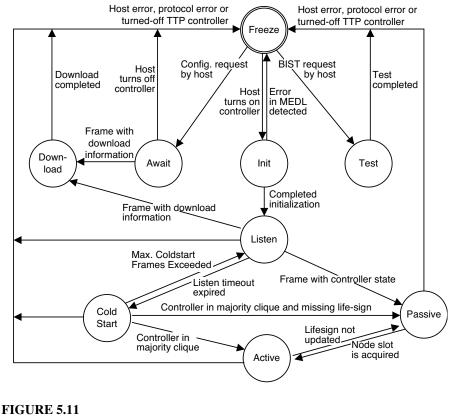

|   | 5.5         | Protoc  | ol States                                               | 114 |

|   | 5.6         | Valida  | tion and Verification Efforts                           | 116 |

|   |             | 5.6.1   | Formal Analysis of Clock Synchronization Algorithm      | 116 |

|   |             | 5.6.2   | Formal Analysis of Fault Isolation and Consistency      | 117 |

|   |             | 5.6.3   | Formal Analysis of Membership Service and Clique Avoid- |     |

|   |             |         | ance                                                    | 117 |

|   |             | 5.6.4   | Fault Injection Experiments                             | 118 |

|   | 5.7         |         | ble Configurations and Implementations                  | 119 |

| 6 | Flex        | Pov     |                                                         | 121 |

| U |             | •       | m and K. Bilic                                          | 141 |

|   | 6.1         |         | col Overview                                            | 122 |

|   | 6.2         |         | ol Services                                             | 122 |

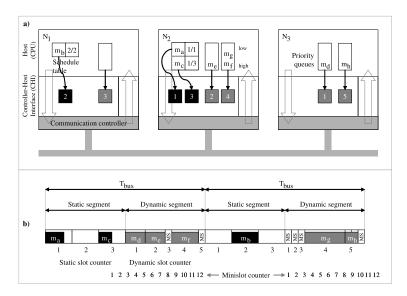

|   |             |         | Communication Services                                  | 122 |

|   |             |         |                                                         |     |

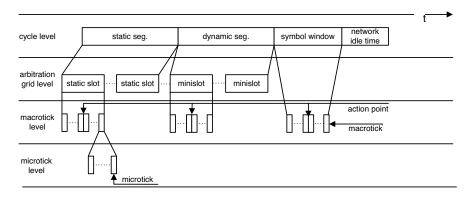

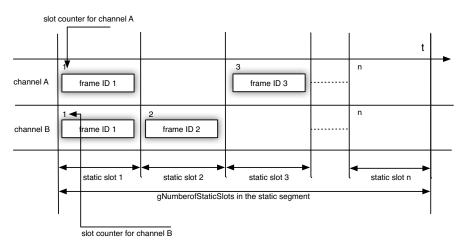

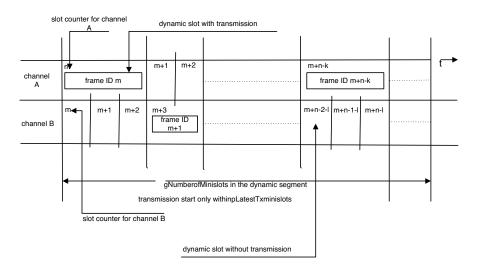

|   |     |        | 6.2.1.1      |                           | 123        |

|---|-----|--------|--------------|---------------------------|------------|

|   |     |        | 6.2.1.2      | Frame Format              | 126        |

|   |     |        | 6.2.1.3      |                           | 129        |

|   |     | 6.2.2  | Protocol     | Operation Control         | 130        |

|   |     | 6.2.3  |              |                           | 132        |

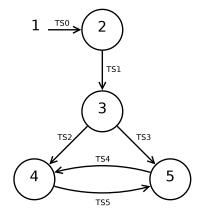

|   |     |        | 6.2.3.1      | Global and Local Time     | 132        |

|   |     |        | 6.2.3.2      | Synchronization Process   | 132        |

|   |     | 6.2.4  | Wakeup a     | and Startup               | 134        |

|   |     |        | 6.2.4.1      | Wakeup                    | 134        |

|   |     |        | 6.2.4.2      |                           | 135        |

|   | 6.3 | Diagno | ostic Servio | ces and Fault Isolation   | 137        |

|   |     | 6.3.1  | Redunda      | nt Communication Channels | 137        |

|   |     | 6.3.2  | Bus Guar     | dians                     | 137        |

|   |     |        | 6.3.2.1      | Local Bus Guardian        | 138        |

|   |     |        | 6.3.2.2      | Central Bus Guardian      | 139        |

|   |     | 6.3.3  | Checks o     |                           | 139        |

|   | 6.4 | Protoc |              | *                         | 140        |

|   |     | 6.4.1  |              |                           | 140        |

|   |     | 6.4.2  | Node Par     | ameters                   | 141        |

|   | 6.5 | Contro | oller Host I | nterface                  | 142        |

|   |     | 6.5.1  |              |                           | 142        |

|   |     | 6.5.2  |              |                           | 144        |

|   |     |        | 6.5.2.1      |                           | 144        |

|   |     |        | 6.5.2.2      |                           | 145        |

|   |     |        | 6.5.2.3      | •                         | 146        |

|   | 6.6 | Examp  | ole Configu  |                           | 148        |

|   |     | 6.6.1  |              |                           | 148        |

|   |     |        | 6.6.1.1      |                           | 148        |

|   |     |        | 6.6.1.2      |                           | 149        |

|   |     |        | 6.6.1.3      |                           | 149        |

| 7 | SAE | Ebus   |              |                           | 153        |

| ' |     |        | and K. Dr    |                           | 155        |

|   | 7.1 | SAFE   |              |                           | 154        |

|   | /.1 | 7.1.1  |              |                           | 154<br>154 |

|   | 7.2 |        |              |                           | 154        |

|   | 7.3 |        |              |                           | 155<br>157 |

|   | 1.5 | 7.3.1  |              |                           | 157        |

|   |     | 7.5.1  | 7.3.1.1      |                           | 159        |

|   |     |        | 7.3.1.2      | e                         | 160        |

|   |     |        | 7.3.1.2      |                           | 160<br>161 |

|   |     |        | 7.3.1.3      |                           | 161        |

|   |     | 7.3.2  |              |                           | 162<br>163 |

|   |     | 7.3.3  |              |                           | 163<br>164 |

|   |     | 7.3.4  |              |                           | 164<br>169 |

|   |     | 1.3.4  | Diagnost     |                           | 109        |

|   |     |        | 7.3.4.1    | Debugging Mechanisms                          | 169 |

|---|-----|--------|------------|-----------------------------------------------|-----|

|   |     | 7.3.5  | Fault Isc  |                                               | 170 |

|   |     |        | 7.3.5.1    | Babble Protection                             | 170 |

|   |     |        | 7.3.5.2    | Byzantine Protection                          | 171 |

|   |     |        | 7.3.5.3    | Availability vs. Integrity Trade-Off          | 171 |

|   |     |        | 7.3.5.4    | Zombie Module Protection                      | 172 |

|   |     | 7.3.6  | Configu    | ration Services                               | 172 |

|   |     |        | 7.3.6.1    | Frame Changes                                 | 172 |

|   |     | 7.3.7  | Protocol   | Parameterization                              | 173 |

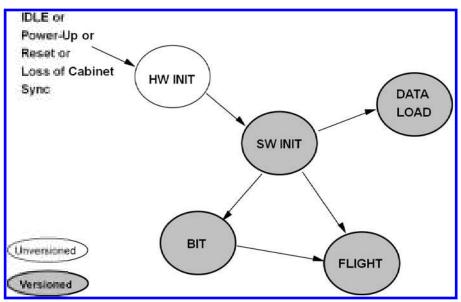

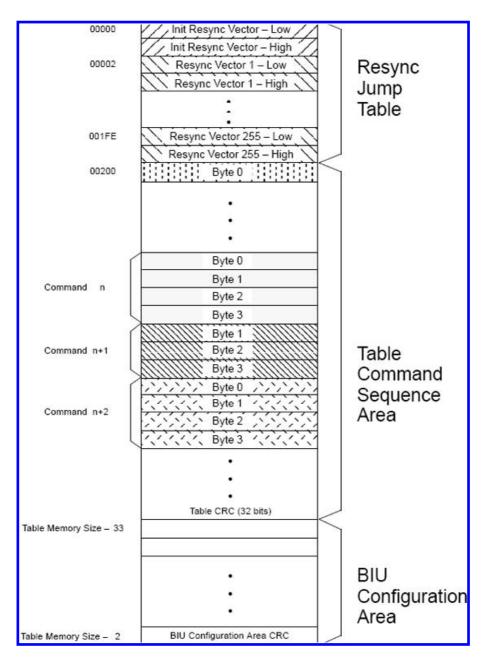

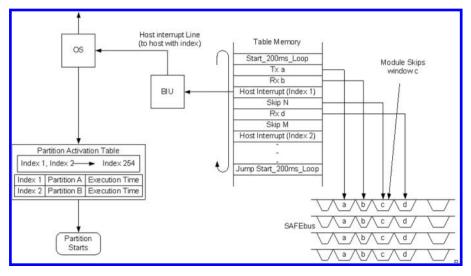

|   |     |        | 7.3.7.1    | Table Memory                                  | 173 |

|   |     |        | 7.3.7.2    | Frame Description Language                    | 174 |

|   |     |        | 7.3.7.3    | Table Versioning                              | 174 |

|   | 7.4 | Comm   | nunication | -                                             | 176 |

|   | 7.5 | Valida | tion and V | Verification Efforts                          | 178 |

|   | 7.6 | Exam   | ole Config | urations and Implementations                  | 178 |

|   |     | -      |            | -                                             |     |

| 8 |     |        | ered Ethe  |                                               | 181 |

|   |     |        |            | B. Hall and M. Paulitsch                      |     |

|   | 8.1 |        | ol Overvie |                                               | 182 |

|   | 8.2 |        |            | S                                             | 184 |

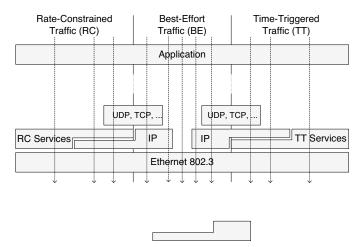

|   |     | 8.2.1  |            | nication Services                             | 185 |

|   |     |        | 8.2.1.1    | Communication Modes                           | 185 |

|   |     |        | 8.2.1.2    | Frame Formats                                 | 187 |

|   |     |        | 8.2.1.3    | Coding and Decoding                           | 190 |

|   |     |        | 8.2.1.4    | Media Access Control                          | 190 |

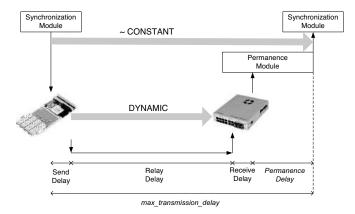

|   |     |        | 8.2.1.5    | Permanence Function                           | 195 |

|   |     | 8.2.2  | Clock S    | ynchronization                                | 196 |

|   |     |        | 8.2.2.1    | Clock Synchronization Overview                | 196 |

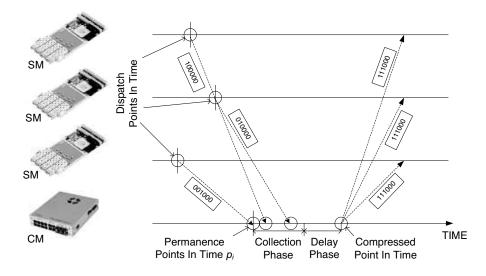

|   |     |        | 8.2.2.2    | First Step Convergence: Compression Master    | 197 |

|   |     |        | 8.2.2.3    | Second Step Convergence: Synchronization Mas- |     |

|   |     |        |            | ter                                           | 200 |

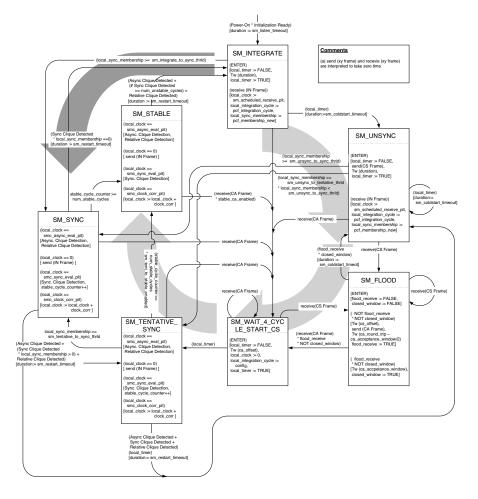

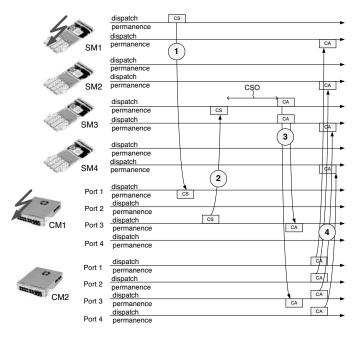

|   |     | 8.2.3  | Startup a  | and Restart                                   | 201 |

|   |     |        | 8.2.3.1    | Integration                                   | 203 |

|   |     |        | 8.2.3.2    | Coldstart                                     | 204 |

|   |     |        | 8.2.3.3    | Restart                                       | 205 |

|   |     |        | 8.2.3.4    | Clique Detection                              | 205 |

|   |     | 8.2.4  | Diagnos    | tic Services                                  | 206 |

|   |     | 8.2.5  | Fault Isc  | lation                                        | 207 |

|   |     |        | 8.2.5.1    | Central Guardian                              | 207 |

|   |     |        | 8.2.5.2    | High-Integrity Design                         | 209 |

|   |     | 8.2.6  | Configur   | ration Services                               | 210 |

|   | 8.3 | Protoc | ol Parame  | terization                                    | 210 |

|   |     | 8.3.1  |            | Topology                                      | 210 |

|   |     | 8.3.2  |            | -Control Flow Parameterization                | 211 |

|   |     | 8.3.3  | Dataflow   | Parameterization                              | 211 |

|    |       | 8.3.3.1 Time-Triggered Parameters                           | 212 |

|----|-------|-------------------------------------------------------------|-----|

|    |       | 8.3.3.2 Rate-Constrained Parameters                         | 212 |

|    |       | 8.3.3.3 Best-Effort Parameters                              | 213 |

|    | 8.4   | Communication Interface                                     | 213 |

|    | 8.5   | Validation and Verification Efforts                         | 214 |

|    |       | 8.5.1 Formal Verification and Analysis                      | 214 |

|    |       | 8.5.2 Certified Development Process                         | 215 |

|    |       | 8.5.3 Model-Based Testing                                   | 215 |

|    | 8.6   | Example Configurations and Implementations                  | 216 |

|    |       | 8.6.1 Configurations                                        | 216 |

|    |       | 8.6.1.1 Master-Based Configuration                          | 216 |

|    |       | 8.6.1.2 Dual-Fault Tolerant Configuration                   | 217 |

|    |       | 8.6.1.3 System-of-Systems Configuration                     | 217 |

|    |       | 8.6.2 Implementations                                       | 219 |

| 9  | TTC   | AN                                                          | 221 |

|    | R. Ka | ammerer                                                     |     |

|    | 9.1   | Protocol Overview                                           | 221 |

|    | 9.2   | Protocol Services                                           | 222 |

|    |       | 9.2.1 Communication Services                                | 222 |

|    |       | 9.2.2 Clock Synchronization                                 | 224 |

|    |       | 9.2.3 Sending and Receiving Messages in TTCAN               | 229 |

|    |       | 9.2.4 Restart, Re-Integration, Integration                  | 230 |

|    |       | 9.2.5 Diagnostic Services                                   | 232 |

|    |       | 9.2.6 Error Detection and Fault Isolation                   | 234 |

|    |       | 9.2.7 Configuration Services                                | 238 |

|    | 9.3   | Protocol Parameterization                                   | 239 |

|    | 9.4   | Communication Interface                                     | 241 |

|    | 9.5   | Validation and Verification Efforts                         | 242 |

|    | 9.6   | Example Configurations and Implementations                  | 243 |

| 10 | LIN   |                                                             | 245 |

|    |       | lmenreich                                                   |     |

|    |       | Protocol Overview                                           | 245 |

|    | 10.2  | Protocol Services                                           | 246 |

|    |       | 10.2.1 Communication Services                               | 246 |

|    | 10.3  | LIN 2.x                                                     | 247 |

|    |       | 10.3.1 Clock Synchronization                                | 248 |

|    |       | 10.3.2 Restart, Re-Integration, Integration                 | 248 |

|    |       | 10.3.3 Diagnostic Services                                  | 248 |

|    |       | 10.3.4 Error Detection and Fault Isolation                  | 249 |

|    |       | 10.3.5 Configuration Services and Protocol Parameterization | 250 |

|    |       | Communication Interface                                     | 252 |

|    |       | Validation and Verification Efforts                         | 253 |

|    | 10.6  | Example Configurations and Implementations                  | 253 |

| 11 | ТТР                                     | /A           |               |                                                | 255 |  |

|----|-----------------------------------------|--------------|---------------|------------------------------------------------|-----|--|

|    | <i>W. E.</i>                            | lmenrei      | ch            |                                                |     |  |

|    | 11.1                                    | Protoco      | ol Overvie    | W                                              | 255 |  |

|    | 11.2                                    | OMG          | Smart Trar    | sducer Standard                                | 256 |  |

|    | 11.3                                    | Interfa      | ce File Sys   | stem (IFS)                                     | 256 |  |

|    |                                         |              |               | 8                                              | 259 |  |

|    |                                         |              |               | ication Services                               | 259 |  |

|    |                                         | 11.4.2       | Clock Sy      | nchronization                                  | 261 |  |

|    |                                         |              |               | Re-Integration, Integration                    | 262 |  |

|    |                                         |              |               | ic Services                                    | 262 |  |

|    |                                         |              | Fault Iso     |                                                | 263 |  |

|    |                                         |              |               | ation Services and Protocol Parameterization   | 263 |  |

|    | 11.5                                    |              | unication     |                                                | 264 |  |

|    |                                         |              |               | erification Efforts                            | 265 |  |

|    |                                         |              |               | urations and Implementations                   | 265 |  |

|    |                                         | 11.7.1       | TTP/A S       | lave Nodes                                     | 265 |  |

|    |                                         |              |               | Iaster                                         | 266 |  |

|    |                                         |              |               |                                                |     |  |

| 12 | BRA                                     |              | <b>D XX U</b> |                                                | 269 |  |

|    | M. Paulitsch, B. Hall and K.R. Driscoll |              |               |                                                |     |  |

|    | 12.1                                    |              |               | W                                              | 270 |  |

|    |                                         |              |               | nent History and Design Goals                  | 270 |  |

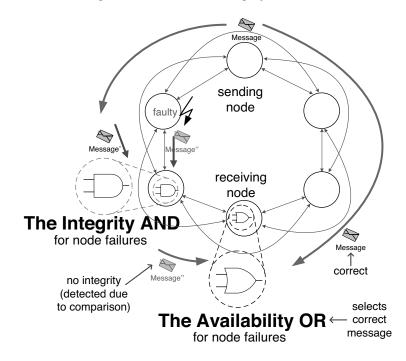

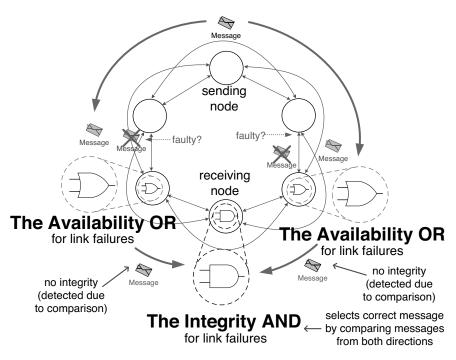

|    |                                         |              |               | Overhead Replication and Input Agreement       | 273 |  |

|    | 12.2                                    |              |               | isms and Services                              | 274 |  |

|    |                                         | 12.2.1       | -             | egrity Data Propagation                        | 274 |  |

|    |                                         |              | 12.2.1.1      |                                                | 274 |  |

|    |                                         |              | 12.2.1.2      | Independent Path Data Integrity Reconstitution | 276 |  |

|    |                                         |              | 12.2.1.3      | Self-Checking Processor Pair Broadcast         | 277 |  |

|    |                                         | 12.2.2       | -             | nchronization, Startup and Clique Resolution   | 279 |  |

|    |                                         |              | 12.2.2.1      | Self-Checking Master Coordination              | 281 |  |

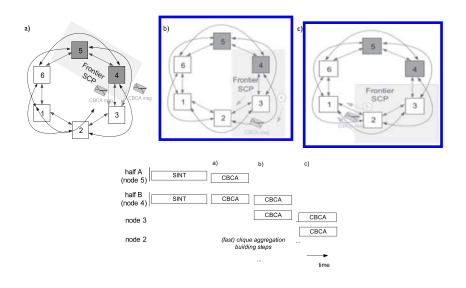

|    |                                         |              | 12.2.2.2      | Connectivity Building and Clique Aggregation   | 282 |  |

|    |                                         |              | 12.2.2.3      | Synchronous Mode Clique Aggregation Break-     |     |  |

|    | 10.0                                    | <b>F</b> 1/1 | 1             | through                                        | 285 |  |

|    | 12.3                                    |              | solation      |                                                | 286 |  |

|    |                                         | 12.3.1       |               | ggered Sequenced Guardian Roles                | 286 |  |

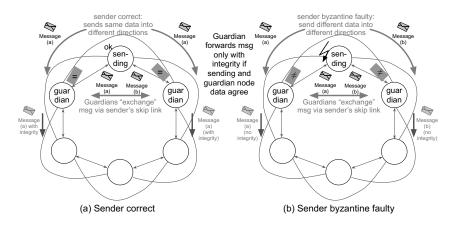

|    |                                         |              | 12.3.1.1      | Directional Integrity Exchange                 | 287 |  |

|    |                                         |              | 12.3.1.2      | Skip Guardian Link Forwarding                  | 288 |  |

|    |                                         |              | 12.3.1.3      | Self-Checking Pair Neighbor Guardian           | 288 |  |

|    |                                         | 12.3.2       |               | onous Guardian Roles                           | 289 |  |

|    |                                         |              | 12.3.2.1      | Startup Enforcement                            | 289 |  |

|    |                                         |              | 12.3.2.2      | Source Authentication                          | 290 |  |

|    |                                         |              | 12.3.2.3      | Additional Guardian Fault Containment Behavior | 291 |  |

|    | 12.4                                    | U            |               | greement Services                              | 291 |  |

|    |                                         | 12.4.1       | Host Tas      | k Set Agreement                                | 291 |  |

|    | 12.6                | -        | le Configurations, Implementations and Deployment Consid-<br>s | 292 |

|----|---------------------|----------|----------------------------------------------------------------|-----|

| 13 | ASC                 | B – Avi  | onics Standard Communications Bus                              | 295 |

|    | <i>M</i> . <i>P</i> | aulitsch |                                                                |     |

|    | 13.1                | Protoco  | ol Overview                                                    | 295 |

|    | 13.2                | Protoco  | ol Services                                                    | 296 |

|    |                     | 13.2.1   | Communication Services                                         | 296 |

|    |                     | 13.2.2   | Clock Synchronization, Restart, Re-Integration and Integra-    |     |

|    |                     |          | tion                                                           | 296 |

|    |                     | 13.2.3   | Diagnostic Services                                            | 299 |

|    |                     | 13.2.4   | Fault Isolation                                                | 299 |

|    |                     | 13.2.5   | Configuration Services                                         | 300 |

|    | 13.3                |          | ol Parameterization                                            | 300 |

|    | 13.4                | Comm     | unication Interface                                            | 300 |

|    | 13.5                | Validat  | ion and Verification Efforts                                   | 301 |

|    | 13.6                | Examp    | le Configurations and Implementations                          | 301 |

| 14 | Indu                | atuial A | nulications                                                    | 303 |

| 14 |                     |          | <b>pplications</b><br>, E. Schmidt, C. Scherrer and H. Kantz   | 303 |

|    |                     |          |                                                                | 304 |

|    |                     |          | Friggered Communication in Aerospace                           | 304 |

|    | 17.2                |          | Requirements                                                   | 305 |

|    |                     |          | A General Discussion of Time-Triggered Communication to        | 505 |

|    |                     | 1 1.2.2  | Meet Requirements                                              | 311 |

|    |                     | 14.2.3   | Use of Time-Triggered Communication Networks in                | 011 |

|    |                     |          | Aerospace and Space                                            | 315 |

|    |                     |          | 14.2.3.1 SAFEbus in Boeing 777                                 | 316 |

|    |                     |          | 14.2.3.2 ASCB in Primus Epic                                   | 321 |

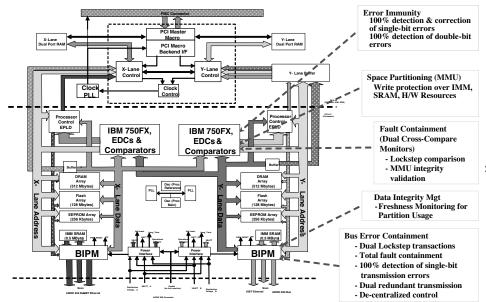

|    |                     |          | 14.2.3.3 Honeywell's Modular Aerospace Controller              | 326 |

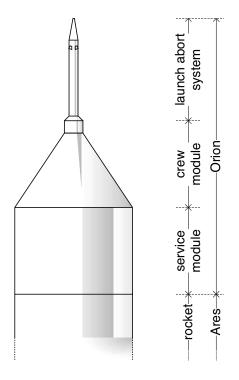

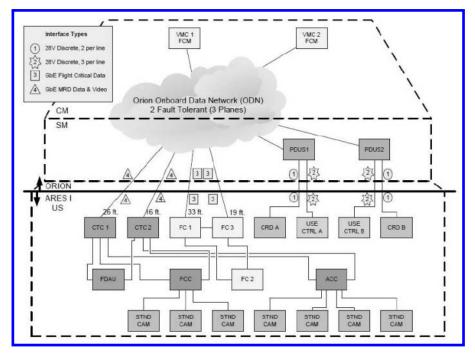

|    |                     |          | 14.2.3.4 TTEthernet in Orion                                   | 328 |

|    | 14.3                | Time-7   | Friggered Communication in Automotive Applications             | 333 |

|    |                     | 14.3.1   |                                                                | 337 |

|    |                     | 14.3.2   |                                                                | 339 |

|    |                     |          | 14.3.2.1 Event-Triggered Approach – FlexRay as CAN Re-         |     |

|    |                     |          | placement                                                      | 340 |

|    |                     |          | 14.3.2.2 Time-Triggered Approach — FlexRay-                    |     |

|    |                     |          | Synchronous Task Execution                                     | 342 |

|    |                     |          | 14.3.2.3 Discussion                                            | 344 |

|    |                     | 14.3.3   | Practical Experience with the Time-Triggered Approach in       |     |

|    |                     |          | Automotive Subsystems                                          | 345 |

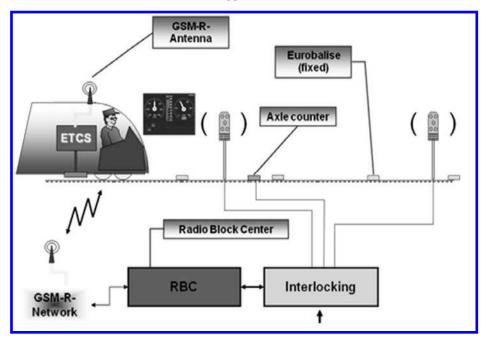

|    | 14.4                | Time-1   | Friggered Communication Services in Railway Applications .     | 346 |

|    |                     |          | Railway Applications                                           | 346 |

|    |                     | 14.4.2   | Requirements on Railway Applications                           | 348 |

|    |                     | 14.4.3   | Requirements on Communication Systems                          | 349 |

xiv

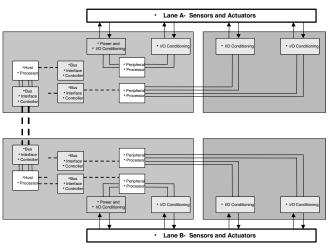

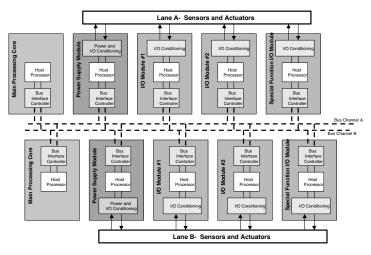

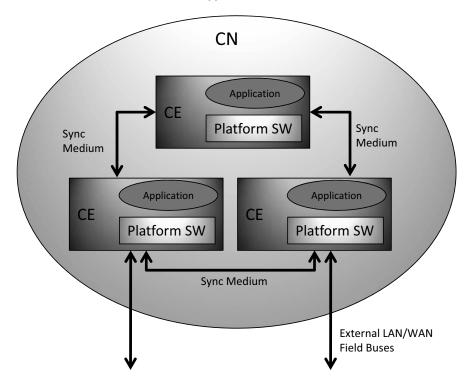

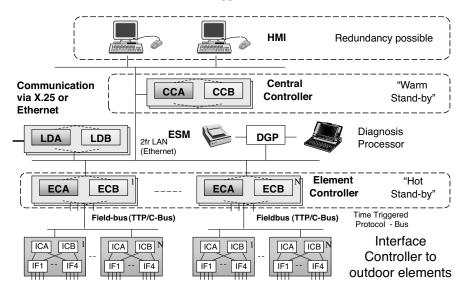

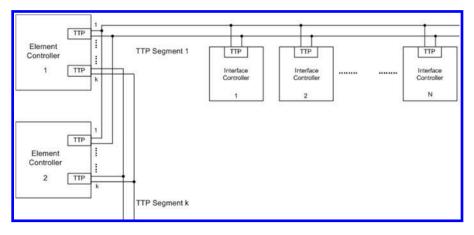

| 1               | 4.4.4 | Generic System Architecture                                | . 350 |

|-----------------|-------|------------------------------------------------------------|-------|

|                 |       | 14.4.4.1 TAS Control Platform Redundancy Architecture      |       |

|                 |       | 14.4.4.2 TAS Control Platform Communication System .       | . 351 |

|                 |       | 14.4.4.3 TAS Control Platform Fault Tolerance Layer        |       |

|                 |       | 14.4.4.4 Connectivity                                      |       |

| 1               | 4.4.5 | Application of Time-Triggered Protocols in the Railway Do  |       |

|                 |       | main                                                       | . 355 |

|                 |       | 14.4.5.1 Interlocking: Architecture (Components, Ser-      | -     |

|                 |       | vices, Interactions)                                       | . 355 |

|                 |       | 14.4.5.2 Field Element Controller                          | . 356 |

|                 |       | 14.4.5.3 Availability Concept                              | . 357 |

| 1               | 4.4.6 | Safety Concept                                             | . 357 |

|                 |       | 14.4.6.1 Timing Requirements                               |       |

|                 |       | 14.4.6.2 TTP-Configuration and Schedule                    |       |

| 1               | 4.4.7 | Conclusion and Outlook                                     | . 359 |

|                 |       |                                                            |       |

| 15 Develo       |       |                                                            | 361   |

| <i>P. Pop</i> , | A. Go | oller, T. Pop and P. Eles                                  | 262   |

|                 |       |                                                            |       |

|                 |       | Tasks                                                      |       |

|                 |       | le Generation                                              |       |

| 1               | 5.3.1 | Requirements and Application Model                         |       |

| 1               | 520   | 15.3.1.1 Application Model                                 |       |

| 1               | 5.3.2 | Scheduling Complexity and Scheduling Strategies            |       |

|                 |       | 15.3.2.1 Incremental Scheduling                            |       |

|                 |       | 15.3.2.2 Host Multiplexing                                 | . 378 |

|                 |       | 15.3.2.3 Dynamic Messaging                                 |       |

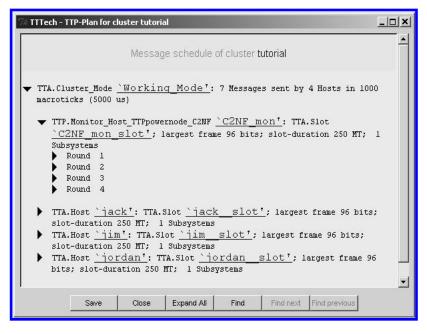

| 1               | 522   | 15.3.2.4 Scheduling Strategies in <sup>TTP</sup> Plan      |       |

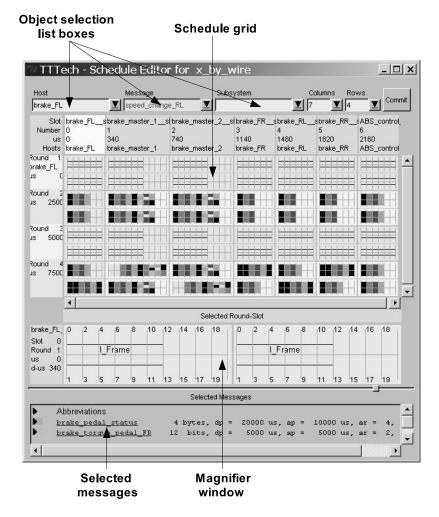

| 1               | 5.3.3 | Schedule Visualization                                     |       |

|                 |       | 15.3.3.1 The Schedule Browser                              |       |

|                 |       | 15.3.3.2 The Schedule Editor                               |       |

|                 |       | 15.3.3.3 The Round-Slot Viewer                             |       |

| 1 <i>5 4</i> T  | T. 1  | 15.3.3.4 Visualization of Message Paths                    |       |

|                 |       | c Scheduling and Optimization                              |       |

|                 |       |                                                            |       |

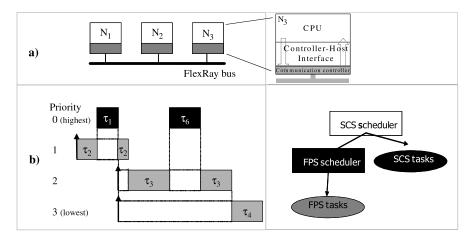

|                 |       | The FlexRay Communication Protocol                         |       |

| 1               |       | Timing Analysis                                            |       |

|                 |       | 15.4.3.1 Schedulability Analysis of DYN Messages           |       |

|                 |       | 15.4.3.2 Holistic Schedulability Analysis of FPS Tasks and |       |

| 4               | 5 1 1 | DYN Messages                                               |       |

| 1               | 3.4.4 | Bus Access Optimization                                    |       |

|                 |       | 15.4.4.1 The Basic Bus Configuration                       |       |

|                 |       | 15.4.4.2 Greedy Heuristic                                  |       |

|                 |       | 15.4.4.3 Simulated Annealing-Based Approach                |       |

|                 |       | 15.4.4.4 Evaluation of Bus Optimization Heuristics         | . 407 |

| 15.5 | Incremental Design |             |                                                  |     |  |  |  |

|------|--------------------|-------------|--------------------------------------------------|-----|--|--|--|

|      |                    |             | aries                                            | 410 |  |  |  |

|      |                    |             | System Architecture                              | 410 |  |  |  |

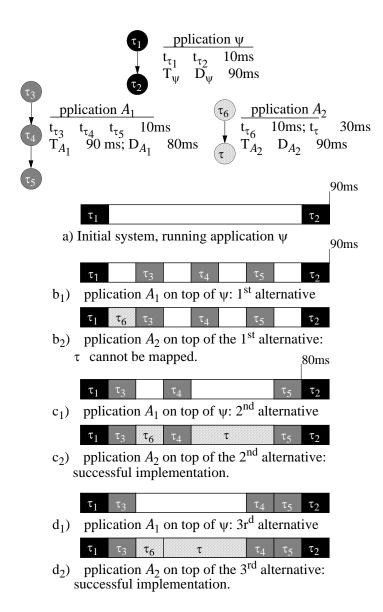

|      |                    | 15.5.1.2    | Application Mapping and Scheduling               | 411 |  |  |  |

|      | 15.5.2             |             | Formulation                                      | 414 |  |  |  |

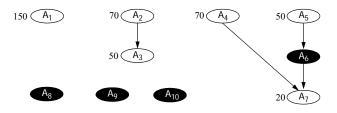

|      | 15.5.3             | Character   | rizing Existing and Future Applications          | 416 |  |  |  |

|      |                    |             | Characterizing the Already Running Applications  | 416 |  |  |  |

|      |                    |             | Characterizing Future Applications               | 418 |  |  |  |

|      | 15.5.4             |             | Metrics and Objective Function                   | 419 |  |  |  |

|      |                    | 15.5.4.1    | 5                                                | 419 |  |  |  |

|      |                    | 15.5.4.2    | Distribution of Slacks (the second criterion)    | 421 |  |  |  |

|      |                    |             | Objective Function and Exact Problem Formula-    |     |  |  |  |

|      |                    |             | tion                                             | 421 |  |  |  |

|      | 15.5.5             | Mapping     | and Scheduling Strategy                          | 422 |  |  |  |

|      |                    | 15.5.5.1    |                                                  | 423 |  |  |  |

|      |                    |             | Iterative Design Transformations                 | 424 |  |  |  |

|      |                    | 15.5.5.3    | •                                                | 427 |  |  |  |

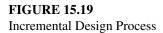

|      | 15.5.6             |             | ental Results                                    | 431 |  |  |  |

|      |                    | 15.5.6.1    |                                                  |     |  |  |  |

|      |                    |             | Design Transformations                           | 431 |  |  |  |

|      |                    | 15.5.6.2    | Evaluation of the Modification Cost Minimization |     |  |  |  |

|      |                    |             | Heuristics                                       | 435 |  |  |  |

| 15.6 | Integra            | tion of Tin | ne-Triggered Communication with Event-Triggered  |     |  |  |  |

|      | Tasks              |             |                                                  | 437 |  |  |  |

|      | 15.6.1             |             | Architecture                                     | 437 |  |  |  |

|      | 15.6.2             |             | tion Problem                                     | 438 |  |  |  |

|      | 15.6.3             |             | bility Analysis                                  | 439 |  |  |  |

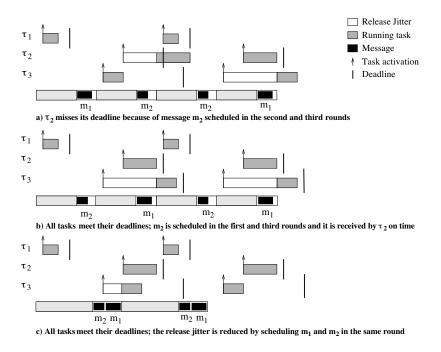

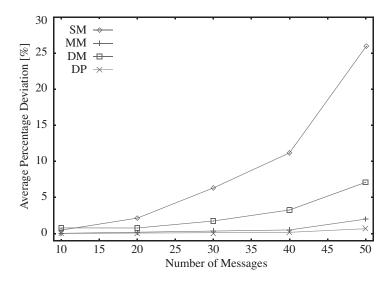

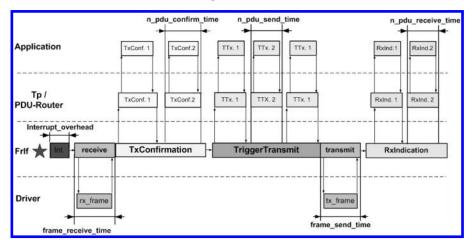

|      |                    |             | Static Single Message Allocation (SM)            | 440 |  |  |  |

|      |                    |             | Static Multiple Message Allocation (MM)          | 442 |  |  |  |

|      |                    |             | Dynamic Message Allocation (DM)                  | 443 |  |  |  |

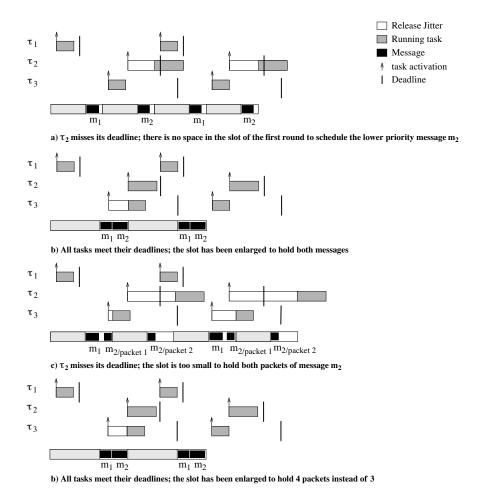

|      |                    |             | Dynamic Packet Allocation (DP)                   | 444 |  |  |  |

|      | 15.6.4             |             | tion Strategy                                    | 446 |  |  |  |

|      |                    | 15.6.4.1    |                                                  | 447 |  |  |  |

|      |                    | 15.6.4.2    | 5                                                | 450 |  |  |  |

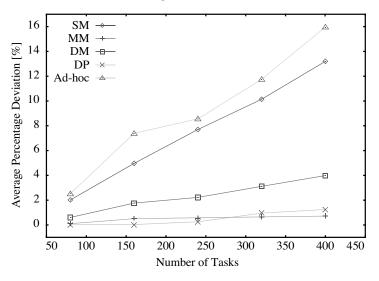

|      | 15.6.5             | Experime    | ental Results                                    | 452 |  |  |  |

| 15.7 |                    |             | d Code Generation                                | 455 |  |  |  |

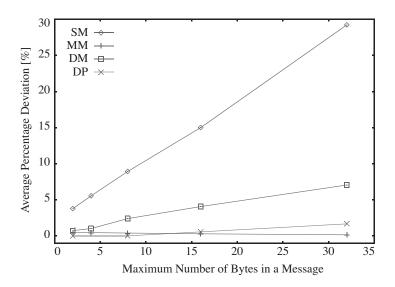

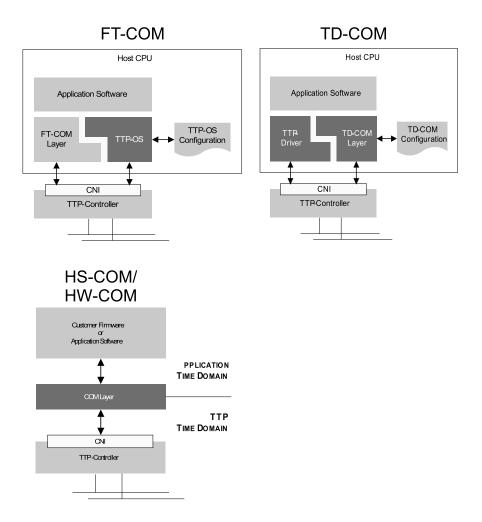

|      |                    |             | ication Configuration                            | 456 |  |  |  |

|      |                    |             | TTP — Personalized MEDLs                         | 456 |  |  |  |

|      |                    | 15.7.1.2    | Monitor MEDL for TTP                             | 457 |  |  |  |

|      |                    | 15.7.1.3    | Buffer Configuration for FlexRay                 | 457 |  |  |  |

|      | 15.7.2             |             | are Configuration                                | 458 |  |  |  |

|      |                    | 15.7.2.1    | Configuration Format                             | 460 |  |  |  |

|      |                    | 15.7.2.2    | FlexRay Interface Configuration                  | 461 |  |  |  |

|      |                    | 15.7.2.3    | HS-COM Configuration                             | 466 |  |  |  |

|      | 15.7.3             |             | neration                                         | 468 |  |  |  |

|               | 15.7.3.1   | Feature Configuration               | 468 |

|---------------|------------|-------------------------------------|-----|

|               | 15.7.3.2   |                                     | 472 |

| 15.7.4        | Configur   | ation of Third-Party Software       | 476 |

| 15.8 Verifica |            |                                     | 477 |

| 15.8.1        |            | Requirements                        | 478 |

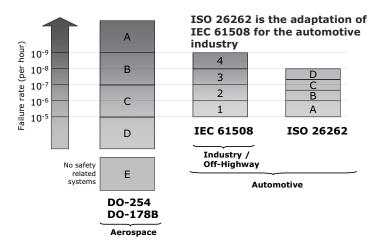

|               | 15.8.1.1   | DO-178B                             | 479 |

|               | 15.8.1.2   | IEC 61508                           | 480 |

|               | 15.8.1.3   | ISO 26262                           | 481 |

| 15.8.2        | Verificati | on Best Practices                   | 482 |

|               | 15.8.2.1   | Reuse of Processes                  | 482 |

|               | 15.8.2.2   | Extending Checklists                | 483 |

|               | 15.8.2.3   | Use of COTS Products                | 483 |

|               | 15.8.2.4   | Modular Certification               | 484 |

|               | 15.8.2.5   | Requirements Management             | 484 |

|               | 15.8.2.6   | Test Vectors                        | 486 |

|               | 15.8.2.7   | Test Suite                          | 486 |

| 15.8.3        | Verificati | on Tooling Approach                 | 486 |

|               | 15.8.3.1   | Output Correctness                  | 486 |

|               | 15.8.3.2   | Manual vs. Automated Verification   | 487 |

|               | 15.8.3.3   | Qualification of Verification Tools | 488 |

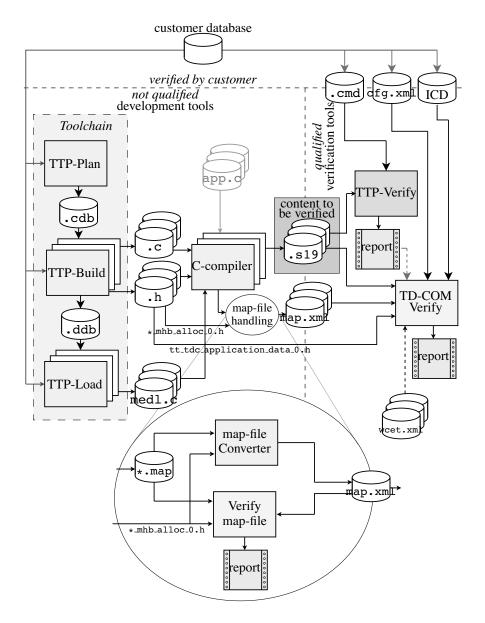

|               | 15.8.3.4   | TTPVerify                           | 489 |

|               | 15.8.3.5   | <sup>TTP</sup> TD-COM-Verify        | 490 |

| bliography    |            |                                     | 495 |

Bibliography

Index

523

## **List of Figures**

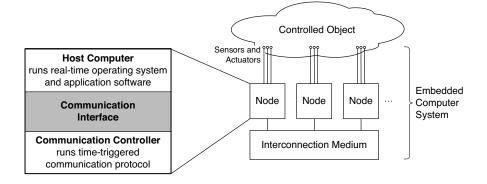

| 2.1  | Embedded Computer System and Internal Structure of a Node                                                                        | 7  |

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

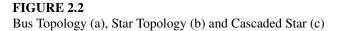

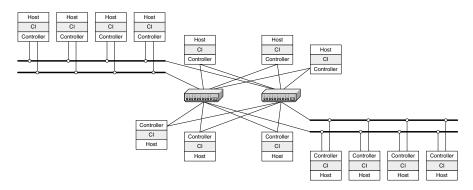

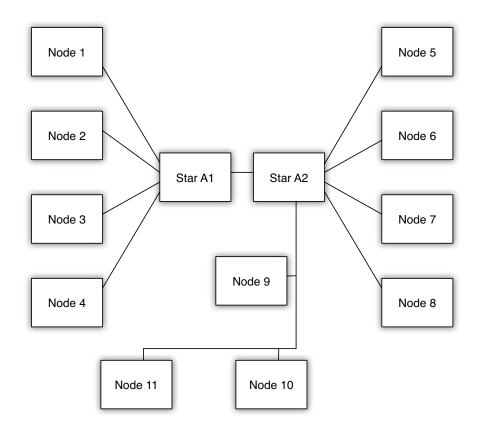

| 2.2  | Bus Topology, Star Topology and Cascaded Star (c)                                                                                | 8  |

| 2.3  | Combination of Star Topology and Bus Topology                                                                                    | 9  |

| 2.4  | Failure Modes of a Physical Clock                                                                                                | 14 |

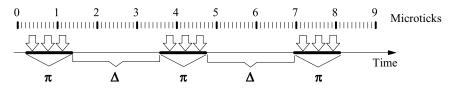

| 2.5  | Sparse Time-Base                                                                                                                 | 18 |

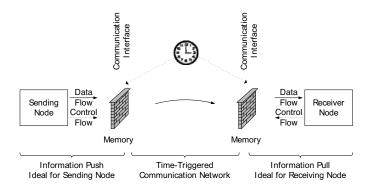

| 2.6  | Data Flow and Control Flow of a Temporal Firewall Interface                                                                      | 22 |

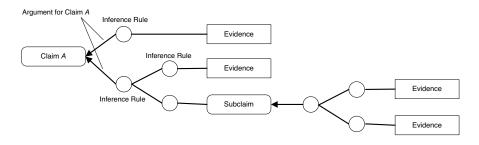

| 3.1  | Hierarchical Structure of a Safety Case with Subclaims                                                                           | 42 |

| 3.2  | Incoming Voting                                                                                                                  | 45 |

| 3.3  | Phase-Alignment between Request Instant and Send Instant of a<br>Periodic Message                                                | 49 |

| 3.4  | Worst-Case Relationship between Request Instant and Send Instant<br>of a Sporadic Message                                        | 50 |

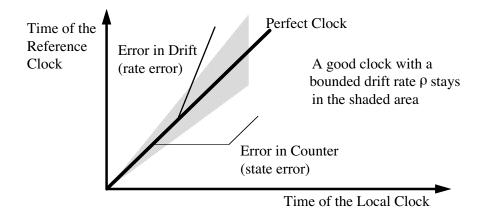

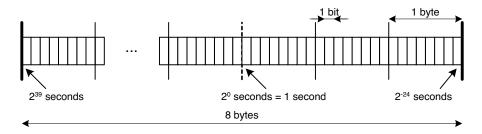

| 4.1  | Optimal Representation of Time in Real-Time Systems                                                                              | 67 |

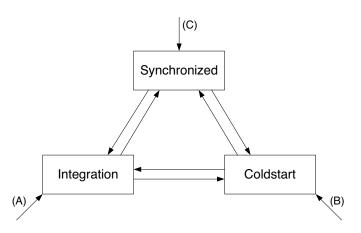

| 4.2  | The Startup/Restart Triangle: A Time-Triggered Protocol Usually<br>Distinguishes between the Integration, the Coldstart, and the |    |

|      | Synchronized Phase                                                                                                               | 69 |

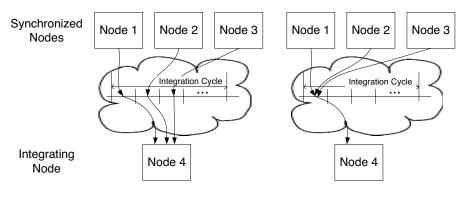

| 4.3  | Integration Messages Must Be Periodically Communicated to                                                                        |    |

|      | Allow Integration; The Integration Messages May Be Sent                                                                          |    |

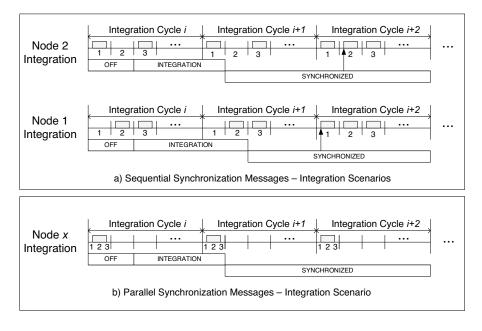

|      | in Sequence or in Parallel                                                                                                       | 71 |

| 4.4  | The Determination of the Number of Synchronized Nodes Can Be<br>Done by "Counting" the Number of Received Integration Messages   |    |

|      | or by Checking the Contents of an Integration Message                                                                            | 73 |

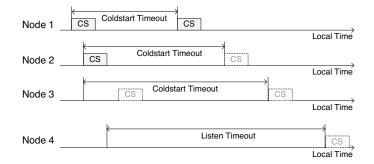

| 4.5  | TTP Coldstart Scenario: Nodes 1 and 2 Produce a Collision, Which                                                                 |    |

|      | is Resolved by Unique Timeouts                                                                                                   | 76 |

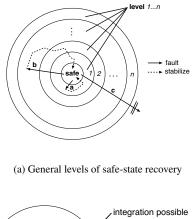

| 4.6  | Different Levels of Safe State Violations and Their Recovery                                                                     |    |

|      | Actions                                                                                                                          | 78 |

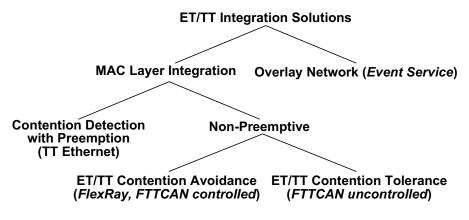

| 4.7  | Solutions for Integration of Event-Triggered and Time-Triggered                                                                  |    |

|      | Communication                                                                                                                    | 80 |

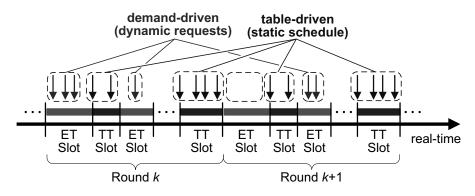

| 4.8  | Event-Triggered and Time-Triggered Communication Slots                                                                           | 82 |

| 4.9  | Subdivision of Communication Slots for an Event-Triggered                                                                        |    |

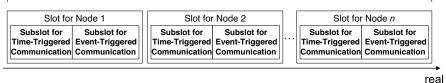

|      | Overlay Network                                                                                                                  | 84 |

| 4.10 | Event-Triggered Overlay Network                                                                                                  | 85 |

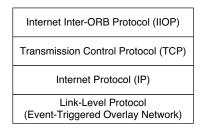

| 4.11 | Commonly Used Protocol Layers for CORBA                                                                                          | 85 |

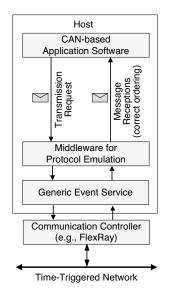

| 4.12 | Node with Middleware for CAN Protocol Emulation                                                                                  | 86 |

xviii

| 5.1         | SAE Network Classes                                       | 94  |

|-------------|-----------------------------------------------------------|-----|

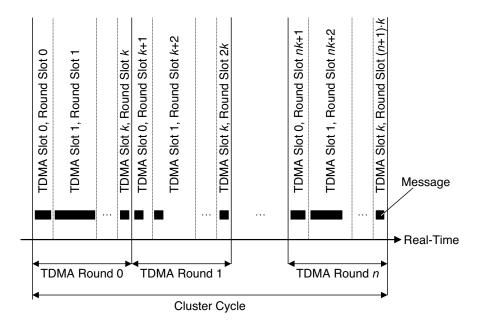

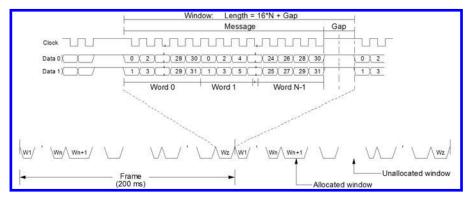

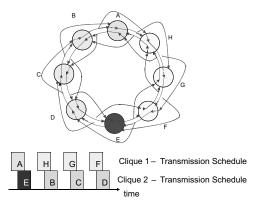

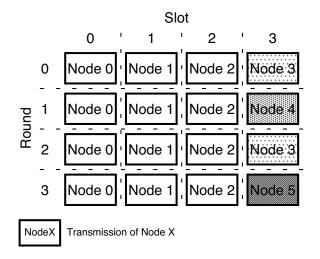

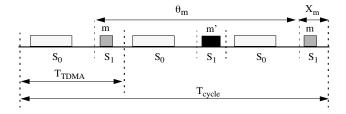

| 5.2         | TDMA Scheme                                               | 97  |

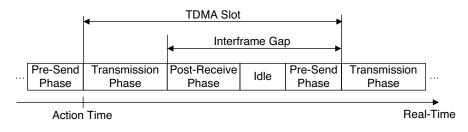

| 5.3         | Timing of a TDMA Slot                                     | 98  |

| 5.4         | Frame Formats                                             | 98  |

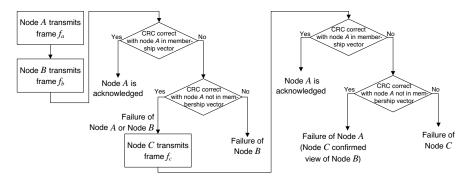

| 5.5         | Acknowledgment Scheme                                     | 102 |

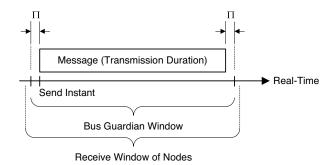

| 5.6         | Bus Guardian Window and Nodes' Receive Window             | 105 |

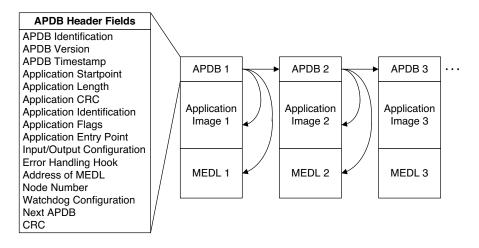

| 5.7         | Application Descriptor Blocks                             | 107 |

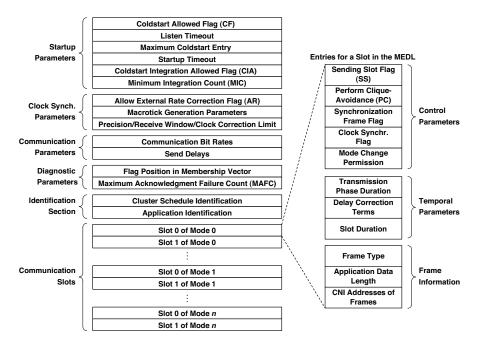

| 5.8         | Layout of the Message Descriptor List                     | 108 |

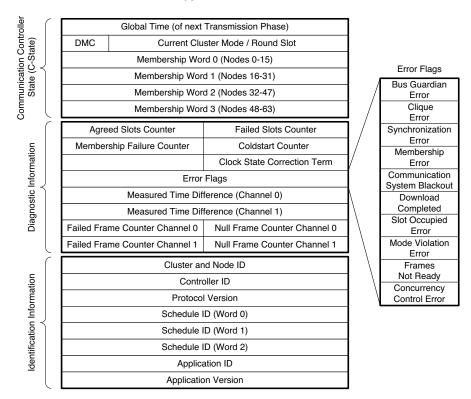

| 5.9         | Layout of Status Area in the CNI of the TTP Communication |     |

|             | Controller C2                                             | 111 |

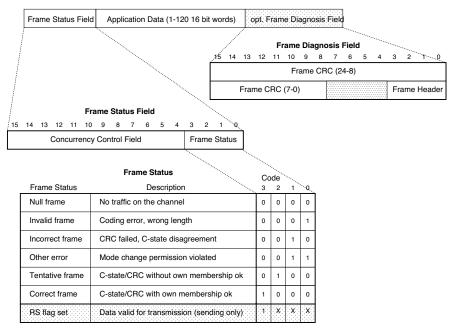

| 5.10        | Application Data and Status Fields in the Message Area    | 115 |

| 5.11        | Protocol States                                           | 116 |

|             |                                                           |     |

| 6.1         | FlexRay Timing Hierarchy                                  | 123 |

| 6.2         | Structure of the Static Segment in FlexRay                | 124 |

| 6.3         | Structure of the Dynamic Segment in FlexRay               | 125 |

| 6.4         | FlexRay Frame Format                                      | 127 |

| 6.5         | FlexRay Coding                                            | 130 |

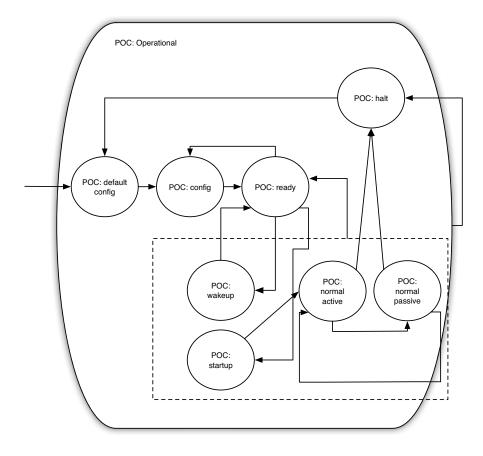

| 6.6         | FlexRay Protocol Operation Control                        | 131 |

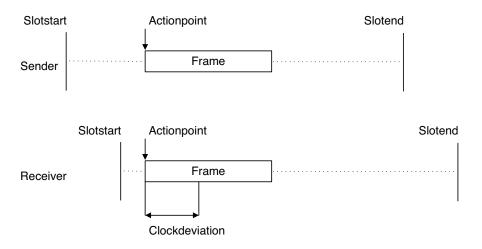

| 6.7         | Deviation of Local Clocks                                 | 132 |

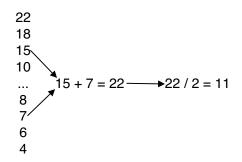

| 6.8         | Fault Tolerant Midpoint Algorithm Used in FlexRay         | 133 |

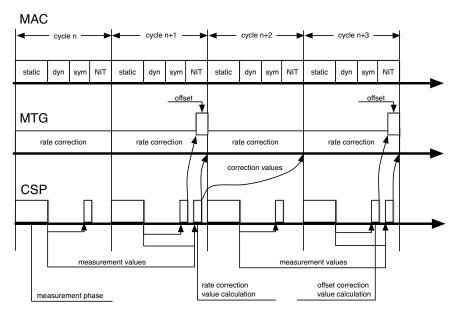

| 6.9         | Clock Synchronization in FlexRay                          | 134 |

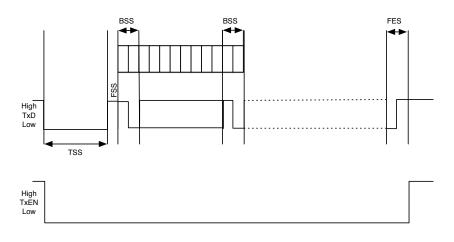

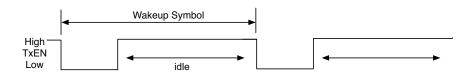

| 6.10        | FlexRay Wakeup Pattern                                    | 135 |

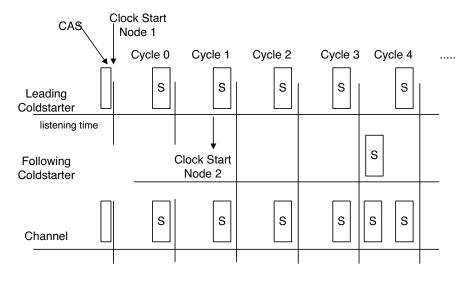

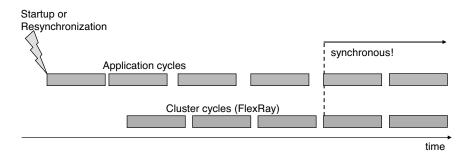

| 6.11        | FlexRay Startup                                           | 136 |

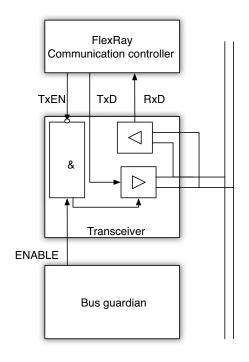

| 6.12        | Local Bus Guardian                                        | 138 |

| 6.13        | Inner Structure of a Central Bus Guardian                 | 139 |

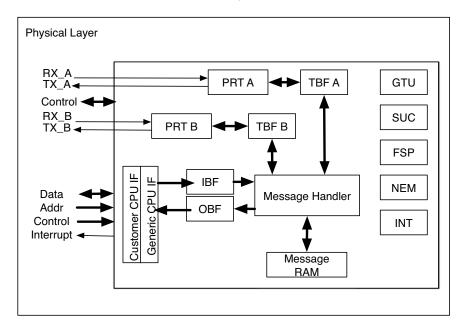

| 6.14        | Block Diagram of the E-Ray Controller                     | 143 |

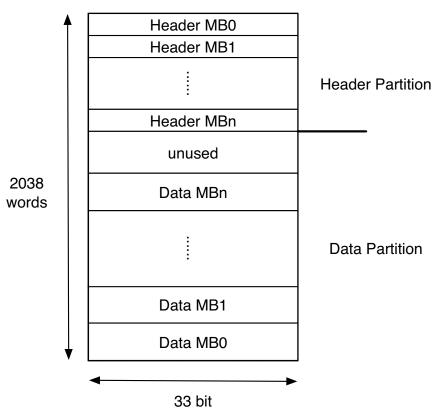

| 6.15        | Assignment of Message Buffers in an E-Ray Controller      | 144 |

| 6.16        | The Message RAM of an E-Ray Controller                    | 145 |

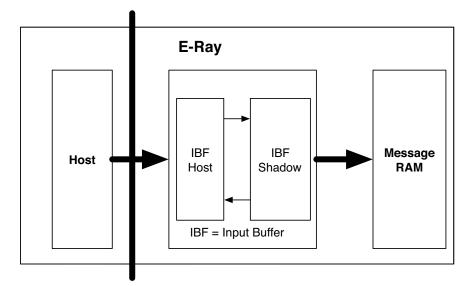

| 6.17        | E-Ray Controller: Input Double Buffer                     | 147 |

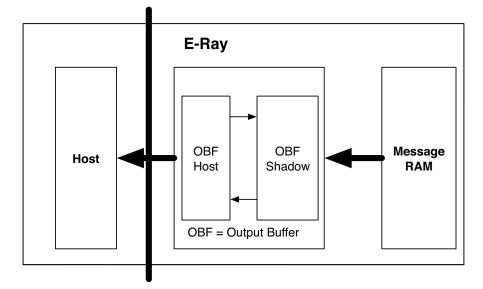

| 6.18        | E-Ray Controller: Output Double Buffer                    | 148 |

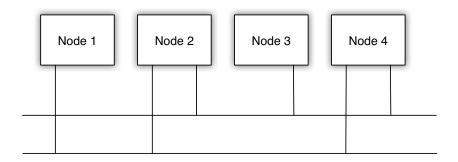

| 6.19        | FlexRay Topologies: Passive Bus Topology                  | 149 |

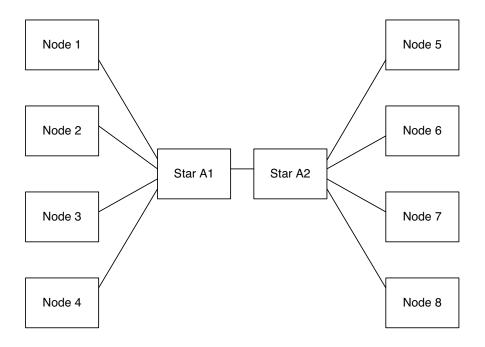

| 6.20        | FlexRay Topologies: Cascaded Stars                        | 150 |

| 6.21        | FlexRay Topologies: Single Channel Hybrid Example         | 151 |

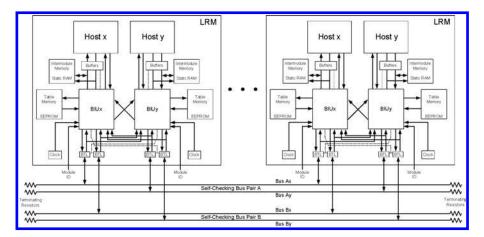

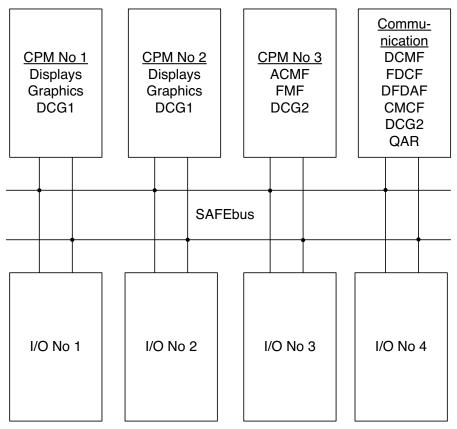

| 7.1         | SAFEbus Interface Logic                                   | 155 |

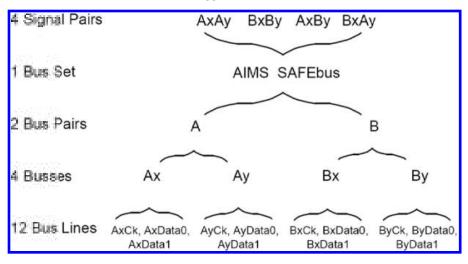

| 7.2         | SAFEbus Nomenclature                                      |     |

| 7.3         | Basic Message Structure                                   |     |

| 7.4         | Master/Shadow Message Structure                           | 161 |

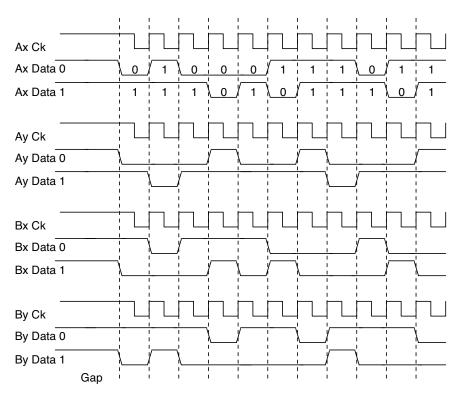

| 7.5         | Bus Encoding Example                                      | 163 |

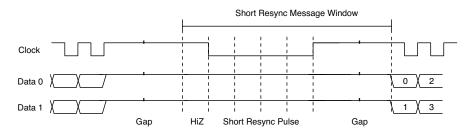

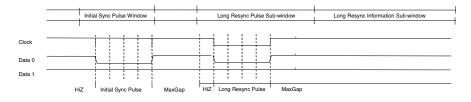

| 7.5<br>7.6  | Short Resync Message                                      | 164 |

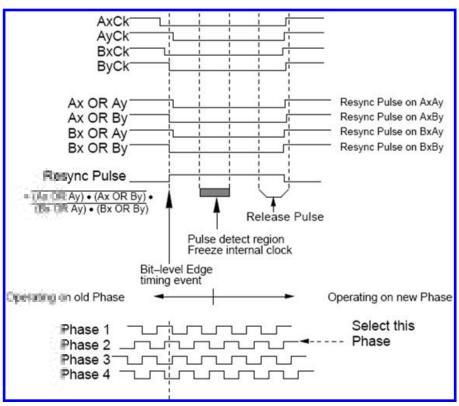

| 7.7         | Resynchronization Pulse Timing                            | 165 |

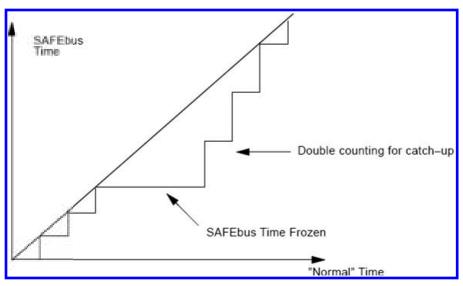

| 7.8         | Time Adjustment                                           | 165 |

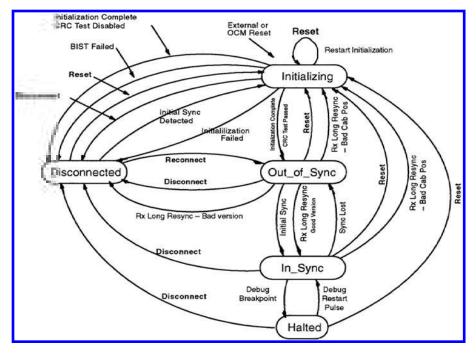

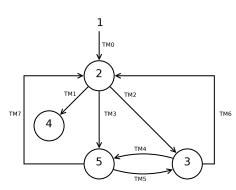

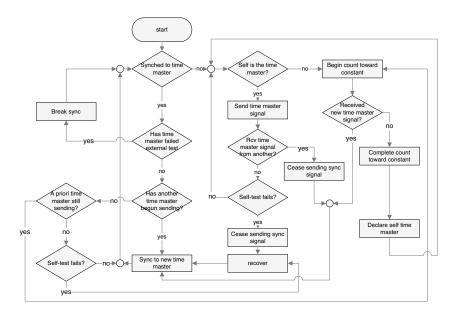

| 7.8<br>7.9  | Synchronization State Diagram                             | 167 |

| 7.9<br>7.10 | Long Resync Message                                       | 167 |

| 1.10        |                                                           | 100 |

| 7.11 | Initial Sync Message                                              | 169 |

|------|-------------------------------------------------------------------|-----|

| 7.12 | Example Frames and Their Frame Change Transitions                 | 174 |

| 7.13 | Table Memory Structure                                            | 175 |

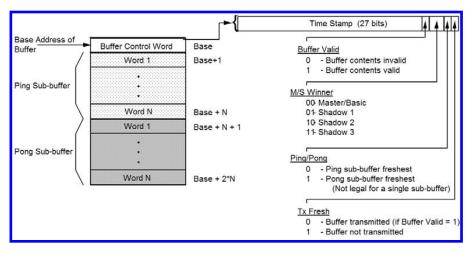

| 7.14 | IMM Buffer Structure                                              | 177 |

| 7.15 | Data Stream Time Partitioning                                     | 178 |

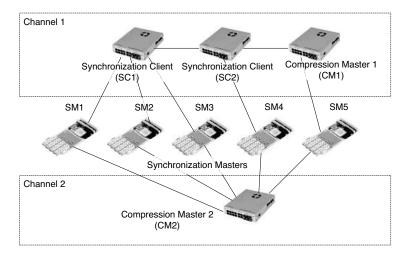

| 8.1  | An Example TTEthernet Network Consisting of Two Channels and      |     |

|      | Five End Systems                                                  | 185 |

| 8.2  | Interaction of Standards                                          | 186 |

| 8.3  | Ethernet Frame Format                                             | 187 |

| 8.4  | Contents of a <i>TTEthernet</i> Protocol Control Frame            | 187 |

| 8.5  | Ethernet Destination Address is Used to Specify the Virtual Link  |     |

|      | Identifier (VL ID) in ARINC 664 Part 7                            | 189 |

| 8.6  | Example Network Topology and Assigned Schedule for the Differ-    |     |

|      | ent Traffic Classes (TT, RC and BE)                               | 191 |

| 8.7  | Integration Methods for High-Priority (H) and Low-Priority (L)    |     |

|      | Traffic                                                           | 192 |

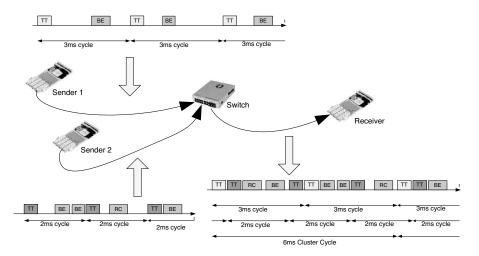

| 8.8  | <i>TTEthernet</i> – Example of Dataflow Integration               | 194 |

| 8.9  | The Permanence Function Transforms Network Jitter into Network    |     |

|      | Latency                                                           | 195 |

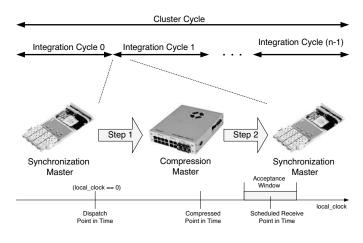

| 8.10 | The Timing Hierarchy in <i>TTEthernet</i>                         | 197 |

| 8.11 | Compression Function Overview                                     | 198 |

| 8.12 | Protocol State Machine for the SMs: Coldstart Proceeds Clockwise, |     |

|      | Regular Integration Counter-Clockwise                             | 202 |

| 8.13 | Startup/Restart Example in Presence of a Faulty SM and a Faulty   |     |

|      | CM: the CA Frame Resolves an Inconsistent Startup Attempt         | 205 |

| 8.14 | Central Guardian Enforcement Actions for Synchronized Time-       |     |

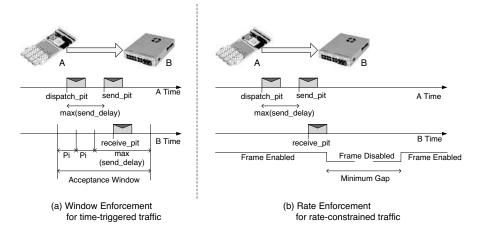

|      | Triggered Traffic and Unsynchronized Rate-Constrained Traffic     | 208 |

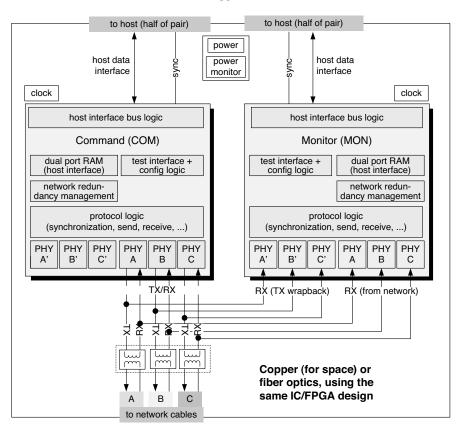

| 8.15 | Realization of a High-Integrity Component as a Comman-            |     |

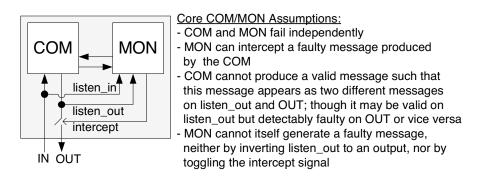

|      | der/Monitor (COM/MON) Architecture                                | 209 |

| 8.16 | Master-Based Configuration with Three Switches Connected in       |     |

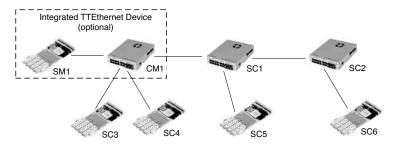

|      | Multi-Hop Topology                                                | 217 |

| 8.17 | Dual-Fault Tolerant Configuration with Three Redundant Channels   |     |

|      | and Five Synchronization Masters                                  | 218 |

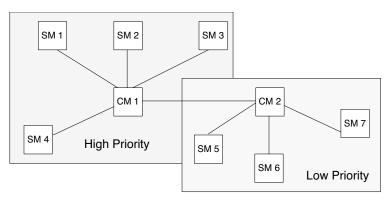

| 8.18 | TTEthernet Systems-of-Systems Configuration Consisting of Two     |     |

|      | Subnetworks                                                       | 218 |

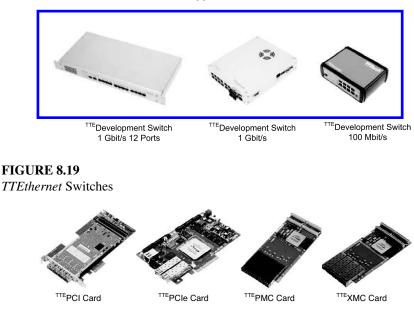

| 8.19 | TTEthernet Switches                                               |     |

| 8.20 | TTEthernet FPGA-Based End Systems in Different Form Factors .     | 220 |

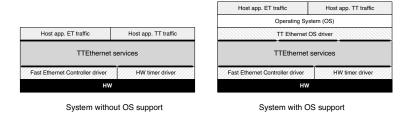

| 8.21 | TTEthernet Software Stack with and without Operating              |     |

|      | Systems Support                                                   | 220 |

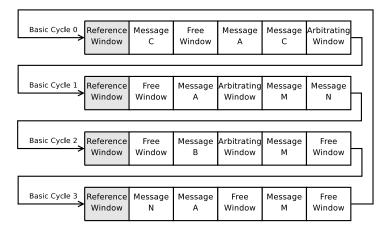

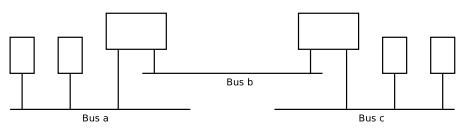

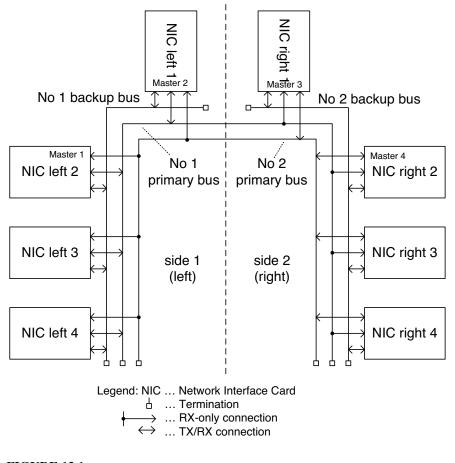

| 9.1  | Basic Cycle in TTCAN                                              | 223 |

| 9.2  | Communication Matrix in TTCAN                                     | 223 |

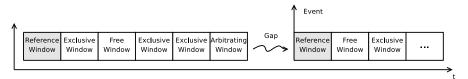

| 9.3  | Event-Synchronized Basic Cycles in TTCAN                          | 224 |

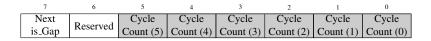

| 9.4  | Reference Message in TTCAN Level 1                                | 225 |

|      | 6                                                                 |     |

| 9.5   | Reference Message in TTCAN Level 2                              | 226 |

|-------|-----------------------------------------------------------------|-----|

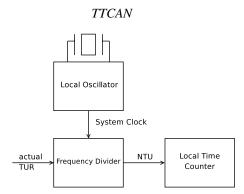

| 9.6   | Local Time Generation in TTCAN                                  | 227 |

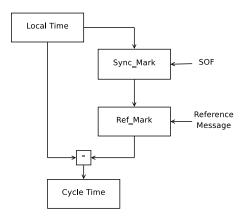

| 9.7   | Cycle Time Generation in TTCAN                                  | 227 |

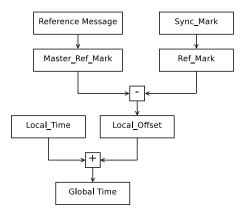

| 9.8   | Global Time Generation in TTCAN                                 | 228 |

| 9.9   | Master/Slave Relation in TTCAN                                  | 231 |

| 9.10  | Synchronization in TTCAN                                        | 232 |

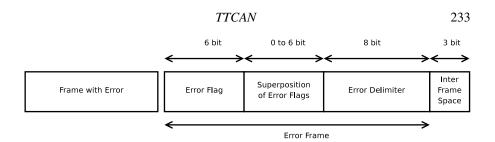

| 9.11  | Error Frame in CAN                                              | 233 |

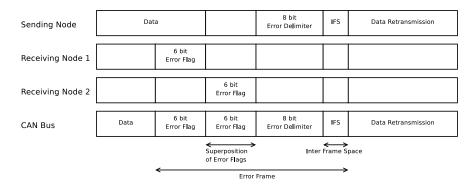

| 9.12  | Error Handling in CAN                                           | 234 |

| 9.13  | System Matrix with Mailbox                                      | 236 |

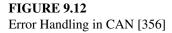

| 9.14  | Coupled TTCAN Buses                                             | 237 |

| 9.15  | Tx_Trigger for Exclusive Message X                              | 240 |

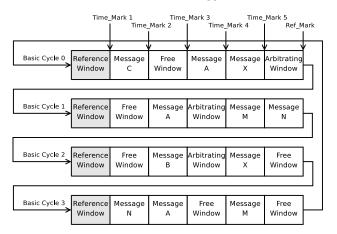

| 10.1  | LIN Frame Format                                                | 246 |

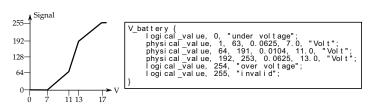

| 10.2  | Example for a LIN Signal Definition                             | 251 |

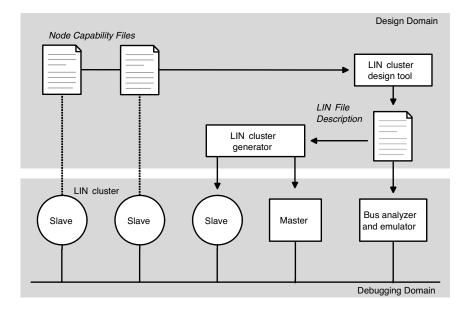

| 10.3  | Development Phases in LIN                                       | 252 |

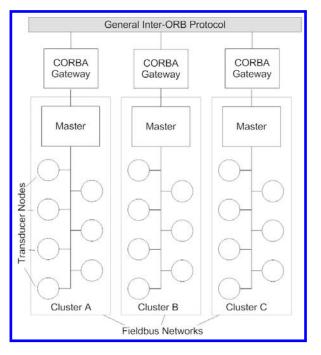

| 11.1  | Multi-Cluster Architecture with CORBA Gateway                   | 257 |

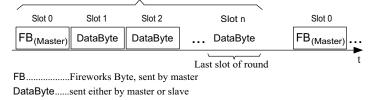

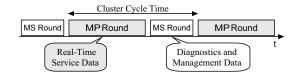

| 11.2  | Example for a TTP/A Multipartner Round                          | 259 |

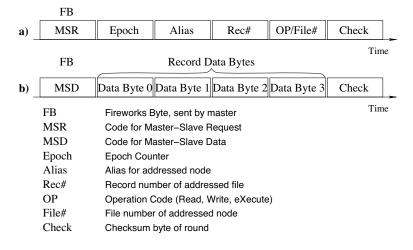

| 11.3  | TTP/A Master/Slave Round                                        | 260 |

| 11.4  | Recommended TTP/A Schedule                                      | 261 |

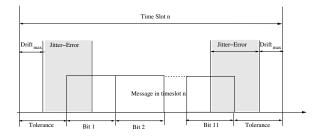

| 11.5  | Tolerance Time in a Slot within a TTP/A Round                   | 261 |

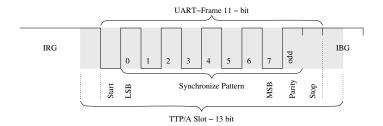

| 11.6  | Synchronization Pattern from TTP/A Master                       | 262 |

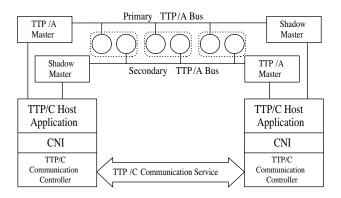

| 11.7  | Integrated Architecture with Two TTP/C Nodes and TTP/A Networks | 263 |

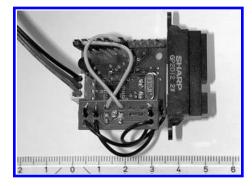

| 11.8  | Smart Transducer Based on Atmel 4433 Microcontroller            |     |

|       | with Distance Sensor Attached                                   | 265 |

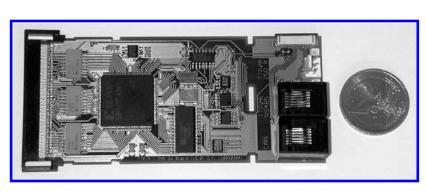

| 11.9  | PCMCIA Gateway Card in Comparison to Size of 2 Euro Coin        | 267 |

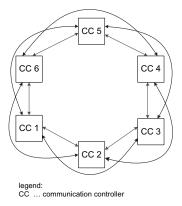

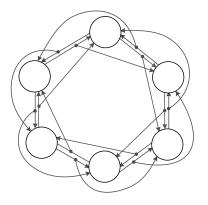

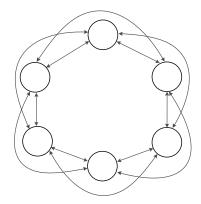

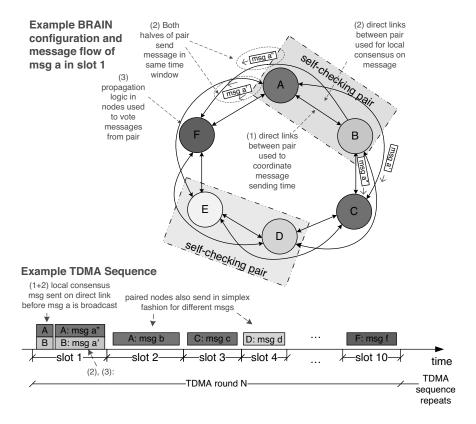

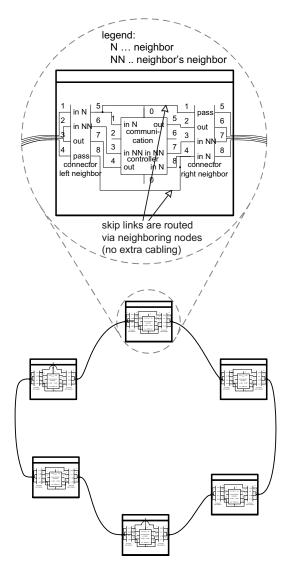

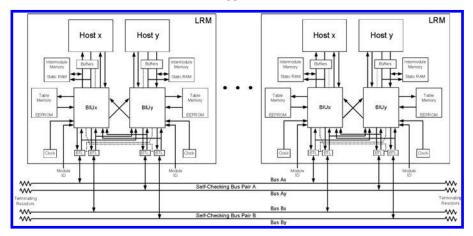

| 12.1  | BRAIN's Braided-Ring Basic Architecture                         | 271 |

| 12.2  | The Two BRAIN Connection Duplex Configurations                  | 272 |

| 12.3  | Conceptual Brain Operation for Tolerating One Arbitrary Fault   | 275 |

| 12.4  | Conceptual BRAIN Operation for a Second Benign Failure          | 277 |

| 12.5  | Self-Checking Pairs                                             | 278 |

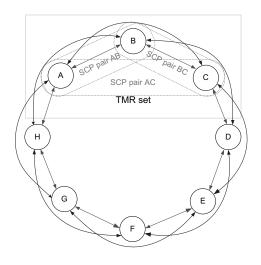

| 12.6  | Triple-Modular Replication (TMR) Deployed on BRAIN              | 280 |

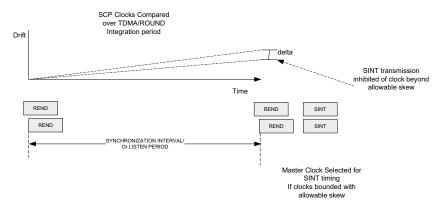

| 12.7  | A Self-Checking Pair Clock Monitoring and Rendezvous            | 282 |

| 12.8  | A BRAIN Clique Scenario                                         | 283 |

| 12.9  | CBCA Link Arbitration Resolves Asynchronous TMDA Clique         |     |

|       | Boundaries                                                      | 284 |

| 12.10 | CBCA Clique Aggregation                                         | 284 |

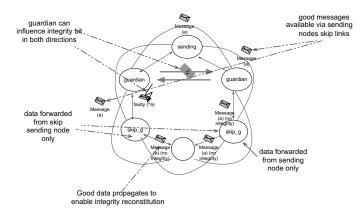

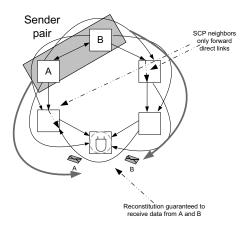

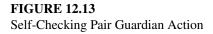

| 12.11 | Consistent Data Guardian Exchange                               | 287 |

| 12.12 | Skip Guardian Action Mitigate                                   | 288 |

| 12.13 | Self-Checking Pair Guardian Action                              | 289 |

| 12.14 | Startup Guardian Action                                         | 290 |

| 12.15 | Cabling of BRAIN Routed within Neighboring Nodes                | 294 |

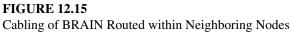

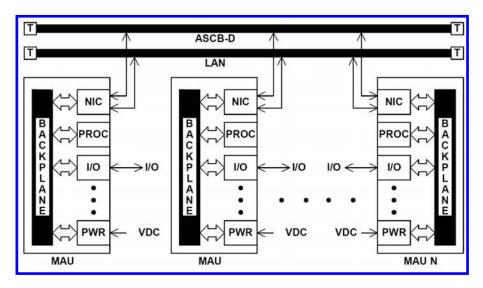

| 13.1  | ASCB Architecture                                               | 297 |

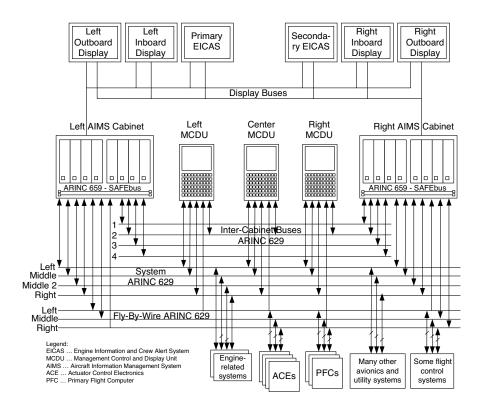

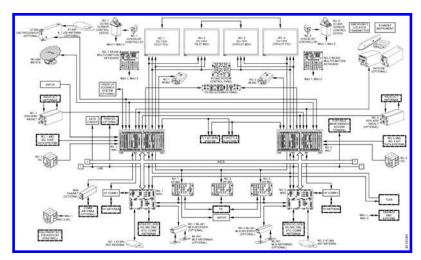

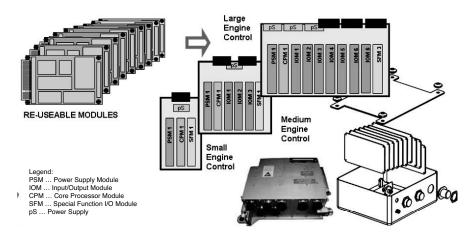

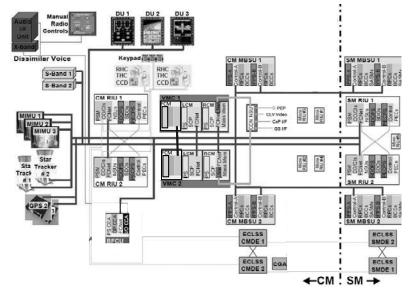

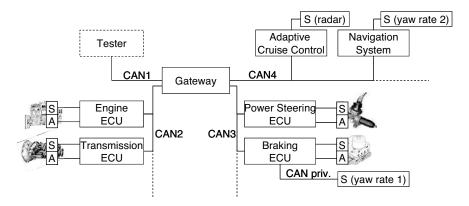

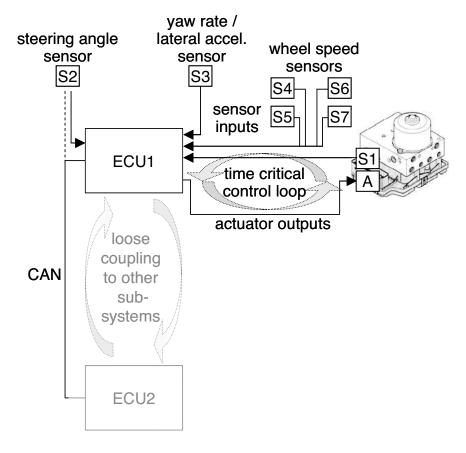

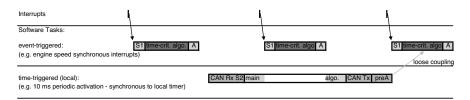

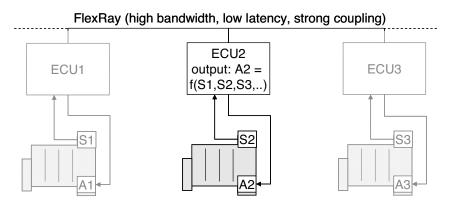

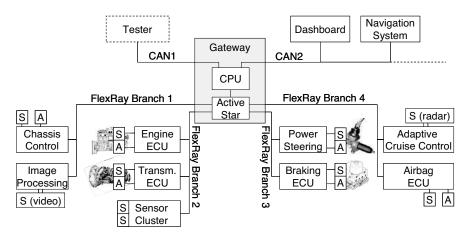

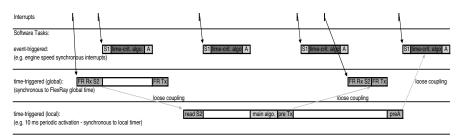

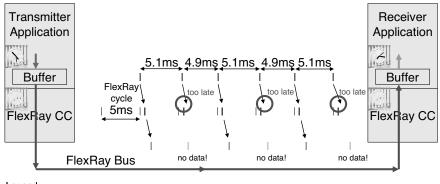

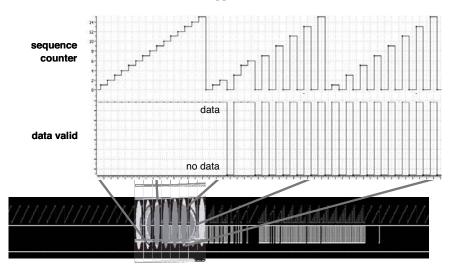

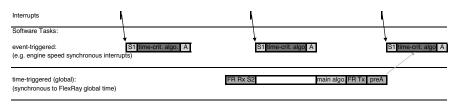

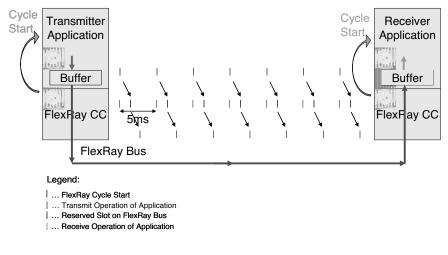

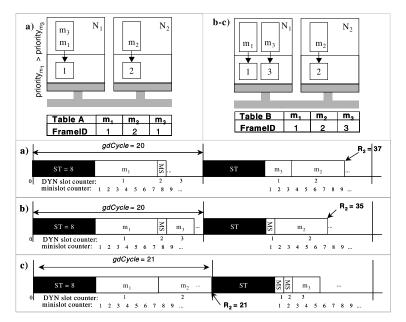

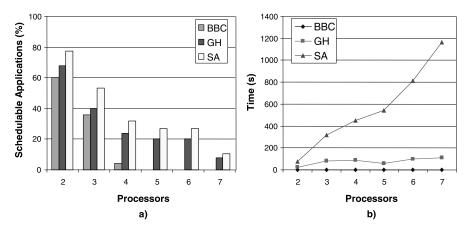

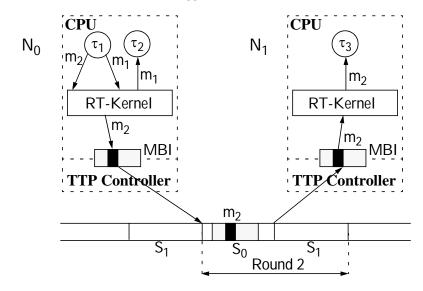

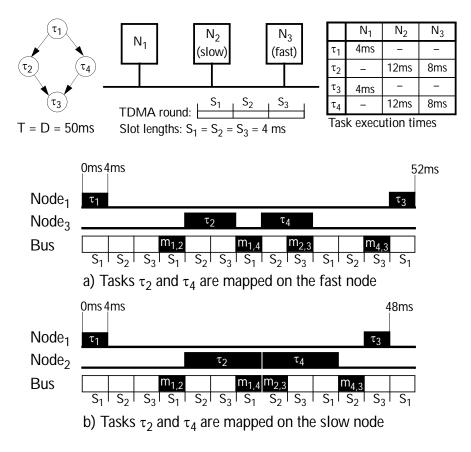

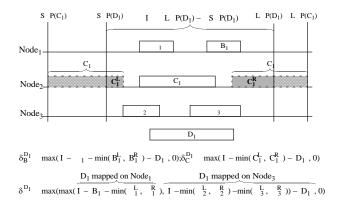

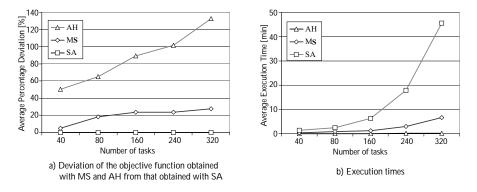

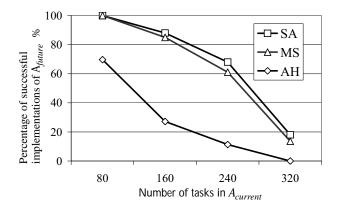

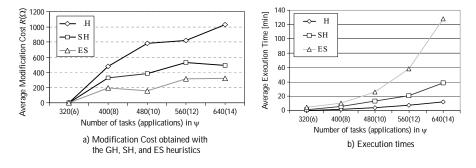

13.2298 13.3 Flow Diagram of ASCB/D Synchronization, Integration and 299 Overview of One AIMS Cabinet Modules and Function Allocation 14.1318 14.2SAFEbus Architecture Overview 319 14.3 320 14.4323 14.5 323 14.6 324 326 14.7 14.8 327 14.9 Sketch of Orion 329 330 331 333 14.13 Orion Avionics Overview 334 335 14.15 336 14.16 Typical Automotive Application Design (CAN-Based) - Timing of 338 14.17 New Automotive Subsystems with FlexRay (CAN-to-FlexRay 339 14.18 Typical New Automotive Systems (CAN + FlexRay) . . . . . . 340 14.19 Adapted Automotive Application Design (Event-Triggered 341 14.20 FlexRay Communication Timing (Event-Triggered Approach) — Transmitter "Asynchronous" to FlexRay - with Lost Messages . . 342 14.21 Practical Measurement Results with an "Asynchronous" Transmit-343 14.22 Rigorous Time-Triggered Automotive Application Design (Time-Triggered Approach) — Timing of Software Execution . . . . . 343 14.23 FlexRay Communication Timing (Time-Triggered Approach) — Transmitter "Synchronous" to FlexRay — without Lost Messages 344 14.24 Smoothly Synchronizing the Local Time to the FlexRay Global 345 347 14.26 TAS Control Platform Redundancy Architecture . . . . . . . . 352 Architecture of the ELEKTRA Interlocking System . . . . . . 14.27 355 357 15.1 Multiplexed Slots 379 15.2 384 15.3 386 15.4388

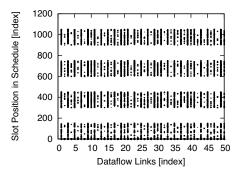

| 15.5  | Illustration of Data Traffic on All Full-Duplex Connections of a             |     |

|-------|------------------------------------------------------------------------------|-----|

|       | TTEthernet Network                                                           | 390 |

| 15.6  | System Architecture Example                                                  | 393 |

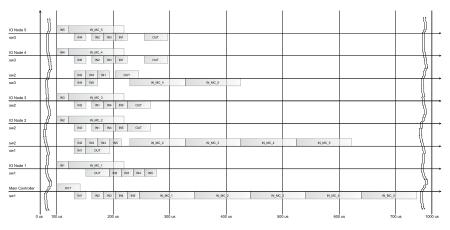

| 15.7  | FlexRay Communication Cycle Example                                          | 394 |

| 15.8  | Global Scheduling Algorithm                                                  | 396 |

| 15.9  | Response Time of a DYN Message                                               | 398 |

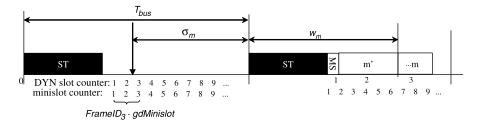

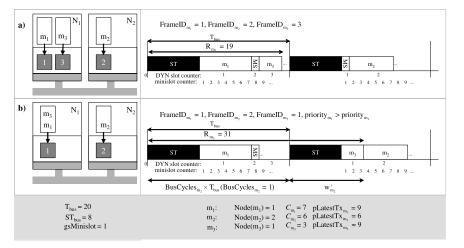

| 15.10 | Transmission Scenarios for DYN Messages                                      | 399 |

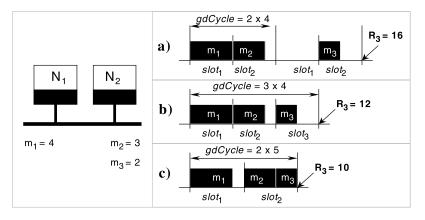

| 15.11 | Optimization of the ST Segment                                               | 402 |

|       | Optimization of the DYN Segment                                              | 403 |

| 15.13 | Basic Bus Configuration                                                      | 404 |

| 15.14 | Greedy Heuristic                                                             | 406 |

| 15.15 | Evaluation of Bus Optimization Algorithms                                    | 408 |

| 15.16 | Message Passing Mechanism                                                    | 410 |

|       | Mapping and Scheduling Example                                               | 412 |

| 15.18 | Application $\mathcal{A}_2$ Implemented on Top of $\Psi$ and $\mathcal{A}_1$ | 415 |

| 15.19 | Incremental Design Process                                                   | 416 |

| 15.20 | Characterizing the Set of Already Running Applications                       | 418 |

|       | Example for the Second Design Criterion                                      | 423 |

| 15.22 | Mapping and Scheduling Strategy (MS)                                         | 424 |

| 15.23 | Step 1 and Step 2 of the Mapping and Scheduling Strategy in Fig-             |     |

|       | ure 15.22                                                                    | 426 |

|       | Successive Steps with Potential Moves for Improving $C_1$                    | 428 |

| 15.25 | Metric for the Subset Selection Heuristic                                    | 430 |

| 15.26 | Evaluation of the Design Transformation Heuristics                           | 434 |

| 15.27 | Percentage of Future Applications Successfully Implemented                   | 435 |

| 15.28 | Evaluation of the Modification Cost Minimization                             | 436 |

| 15.29 | Worst-Case Arrival Time for SM                                               | 441 |

|       | Optimizing the MEDL for SM and MM                                            | 442 |

| 15.31 | Optimizing the MEDL for DM and DP                                            | 445 |

|       | Greedy Heuristic for SM                                                      | 448 |

| 15.33 | Greedy Heuristic for DM                                                      | 450 |

| 15.34 | The Simulated Annealing Strategy                                             | 451 |

|       | Comparison of the Four Approaches to Message Scheduling                      | 453 |

| 15.36 | Four Approaches to Message Scheduling: The Influence of the                  |     |

|       | Number of Messages                                                           | 454 |

| 15.37 | Four Approaches to Message Scheduling: The Influence of the                  |     |

|       | Message Sizes                                                                | 454 |

|       | Examples of Different COM Layers                                             | 459 |

|       | Sending and Receiving on FrIf Level                                          | 463 |

|       | FrIf Configuration as C code — An Example                                    | 465 |

| 15.41 | Communication Configuration as C code — An Example                           |     |

|       | (HS-COM)                                                                     | 467 |

| 15.42 | Comparison of Assurance Levels in Different Certification                    |     |

|       | Standards                                                                    | 481 |

| 15.43 | Interaction of the Development Tools with the Verification Tools $\ .$       | 492 |

## List of Tables

| 4.1<br>4.2<br>4.3 | Classification of clock synchronization algorithms Properties of deterministic clock synchronization algorithms Properties of probabilistic and statistical clock synchronization al- | 62<br>63 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.5               | gorithms                                                                                                                                                                              | 64       |

| 7.1               | SAFEbus terminology                                                                                                                                                                   | 157      |

| 9.1               | CRC—Hamming distance shortfall                                                                                                                                                        | 238      |

| 11.1<br>11.2      | Hierarchical structure of an Interface File System (IFS) address Resource requirements and performance of time-triggered smart                                                        | 258      |

|                   | transducer interface implementations                                                                                                                                                  | 266      |

| 12.1              | SINT message fields                                                                                                                                                                   | 280      |

| 12.2              | CBCA fields                                                                                                                                                                           | 285      |